# **Ti375 Data Sheet**

DSTi375-v1.5 October 2024 www.efinixinc.com

# **Contents**

| Introduction                                              | 4        |

|-----------------------------------------------------------|----------|

| Features                                                  |          |

| Available Package Options                                 | <i>6</i> |

| Device Core Functional Description                        | 7        |

| XLR Cell                                                  |          |

| Embedded Memory                                           | 9        |

| True Dual-Port Mode                                       | 9        |

| Simple Dual-Port Mode                                     |          |

| DSP Block                                                 |          |

| Clock and Control Network                                 |          |

| Clock Sources that Drive the Global and Regional Networks |          |

| Driving the Global Network                                |          |

| Driving the Regional Network                              |          |

| Driving the Local Network                                 | 24       |

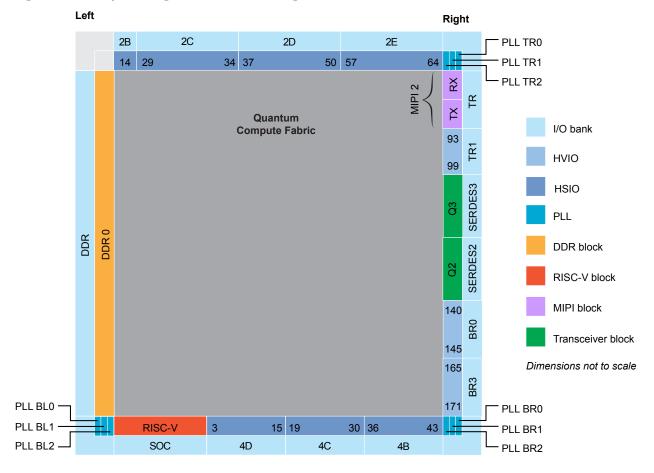

| Device Interface Functional Description                   | 27       |

| Interface Block Connectivity                              |          |

| GPIO                                                      |          |

| Features for HVIO and HSIO Configured as GPIO             | 29       |

| HVIO                                                      | 32       |

| HSIO                                                      |          |

| I/O Banks                                                 | 5C       |

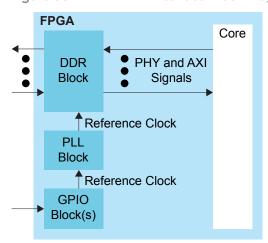

| DDR DRAM Interface                                        |          |

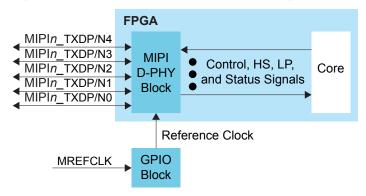

| MIPI D-PHY                                                |          |

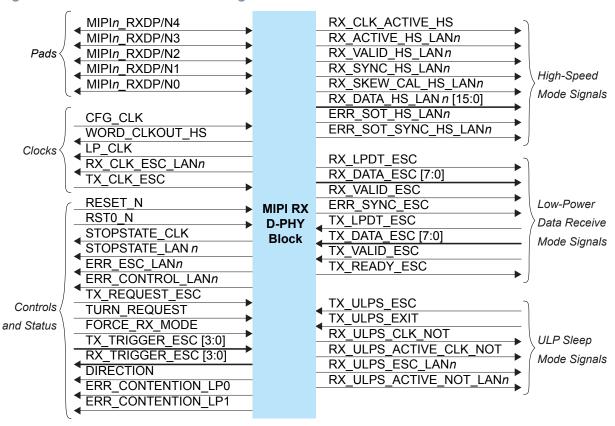

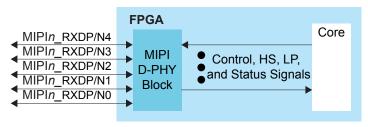

| MIPI RX D-PHY                                             |          |

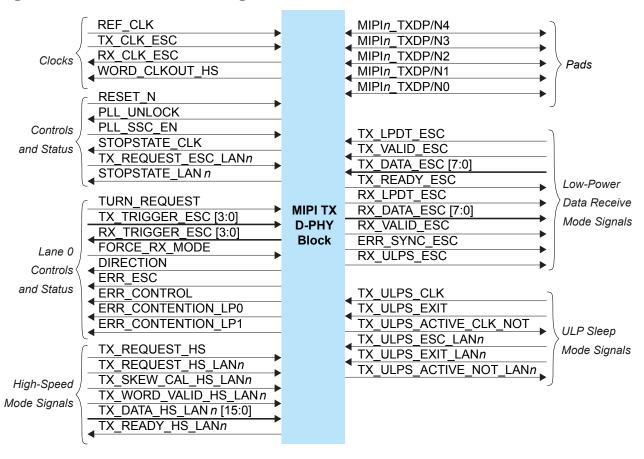

| MIPI TX D-PHY                                             |          |

| Oscillator                                                |          |

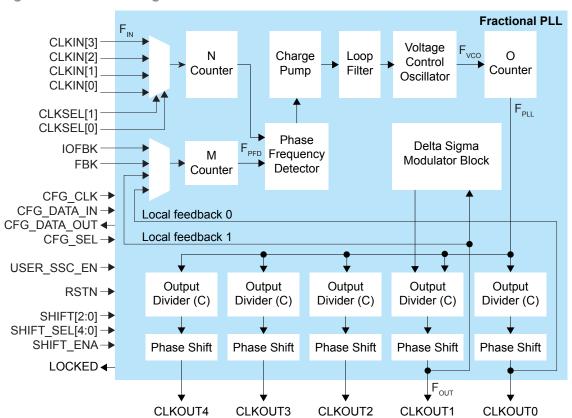

| Fractional PLL                                            |          |

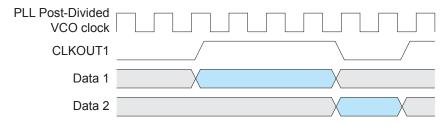

| Programmable Duty Cycle                                   |          |

| Fractional Output Divider                                 |          |

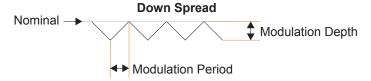

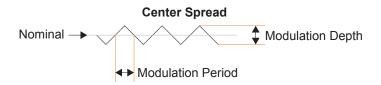

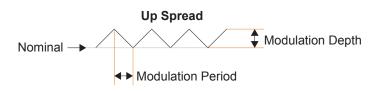

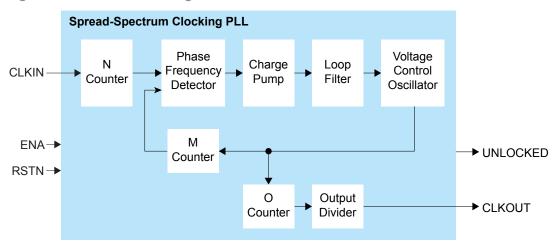

| Spread-Spectrum Clocking                                  |          |

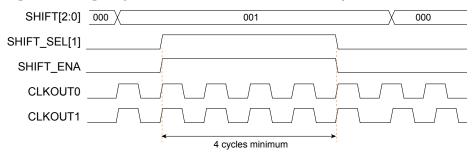

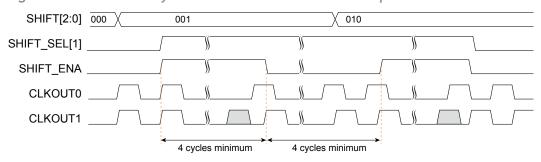

| Dynamic PLL Reconfiguration                               |          |

| Spread-Spectrum Clocking PLL                              |          |

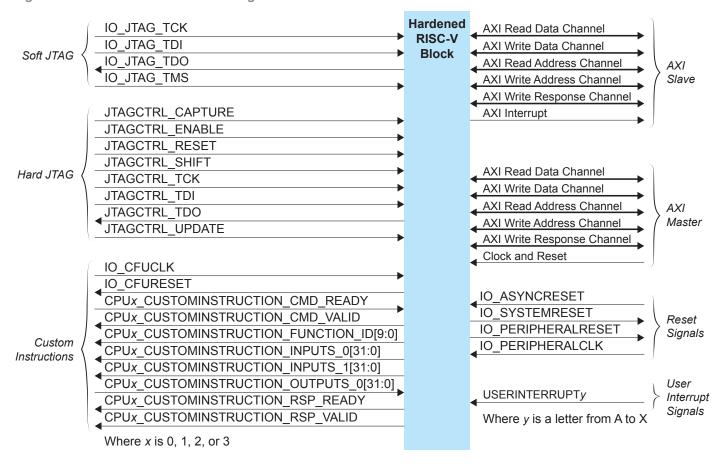

| Hardened RISC-V Block Interface                           |          |

| Transceiver Interface                                     |          |

| Single-Event Upset Detection                              |          |

| Internal Reconfiguration Block                            |          |

| · · · · · · · · · · · · · · · · · · ·                     |          |

| Security Feature                                          | 85       |

| Power Sequence                                            | នន       |

| Power-Up Sequence                                         |          |

| Power-Down Sequence                                       |          |

| Power Supply Current Transient                            |          |

|                                                           |          |

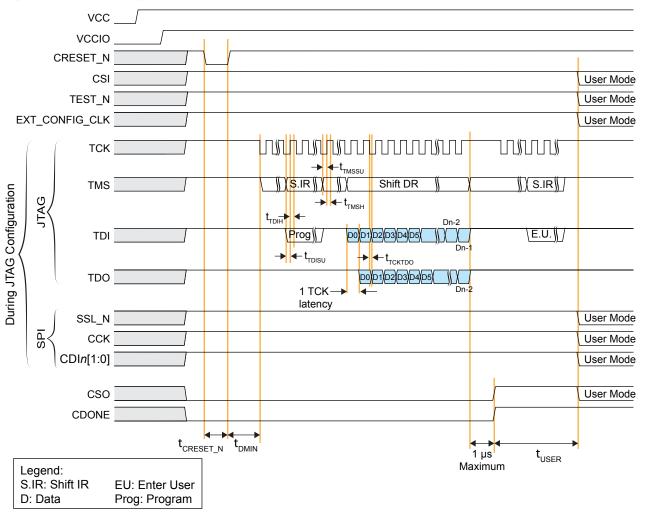

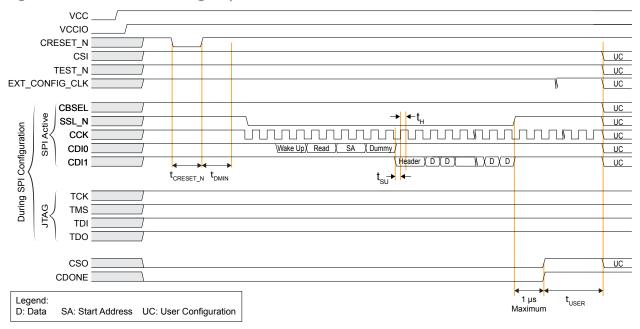

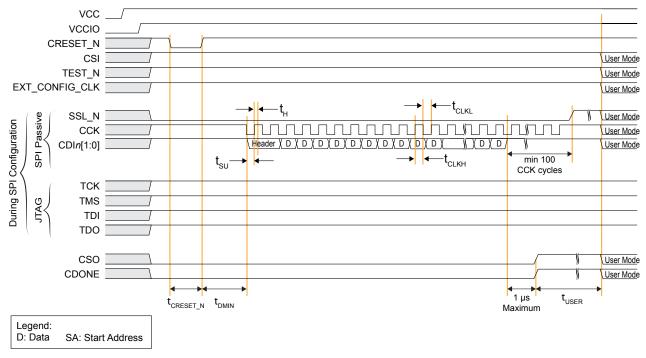

| Configuration                                             |          |

| Supported Configuration Modes                             | 92       |

| Characteristics and Timing                                | 03       |

| DC and Switching Characteristics                          |          |

| HSIO Electrical and Timing Specifications                 |          |

| MIPI Electrical Specifications and Timing                 |          |

| MIPI Reset Timing                                         |          |

| PLL Timing and AC Characteristics                         |          |

| Configuration Timing                                      | 108      |

| Pinout Description           | 113 |

|------------------------------|-----|

| Configuration Pins           | 115 |

| Dedicated DDR Pinout         |     |

| Dedicated MIPI D-PHY Pinout  | 118 |

| Dedicated Transceiver Pinout | 118 |

| Pin States                   | 118 |

| Ti375 Interface Floorplan    | 120 |

| Efinity Software Support     | 122 |

| Ordering Codes               | 123 |

| Revision History             | 123 |

## Introduction

The Titanium Ti375 FPGA features the high-density, low-power Efinix<sup>®</sup> Quantum<sup>®</sup> compute fabric wrapped with an I/O interface. This FPGA has a variety of features, such as a hardened RISC-V block, transceivers, LPDDR4 DRAM controller, and MIPI D-PHY.

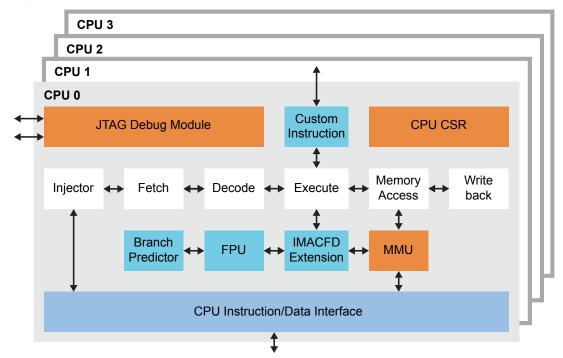

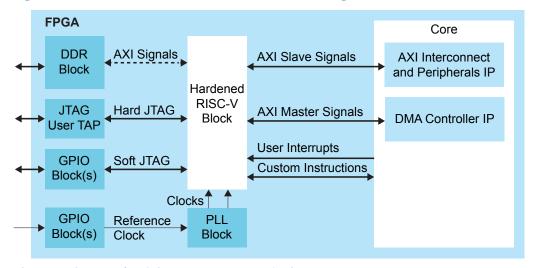

The quad-core hardened RISC-V block has a 32-bit CPU featuring the ISA RISCV32I with M, A, C, F, and D extensions, and six pipeline stages. You utilize the hardened RISC-V block by instantiating the Sapphire High-Performance SoC, combining the speed and efficiency of a hardened RISC-V block with the flexibility of peripherals in soft logic.

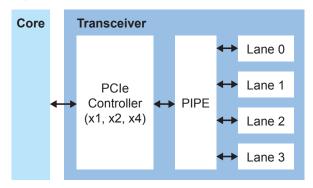

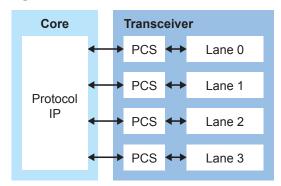

The full-duplex transceivers support multiple protocols including PCIe® Gen4, SGMII, and 10GBase-KR as well as a PMA Direct mode with data rates from 1.25 Gbps to 12.5 Gbps.

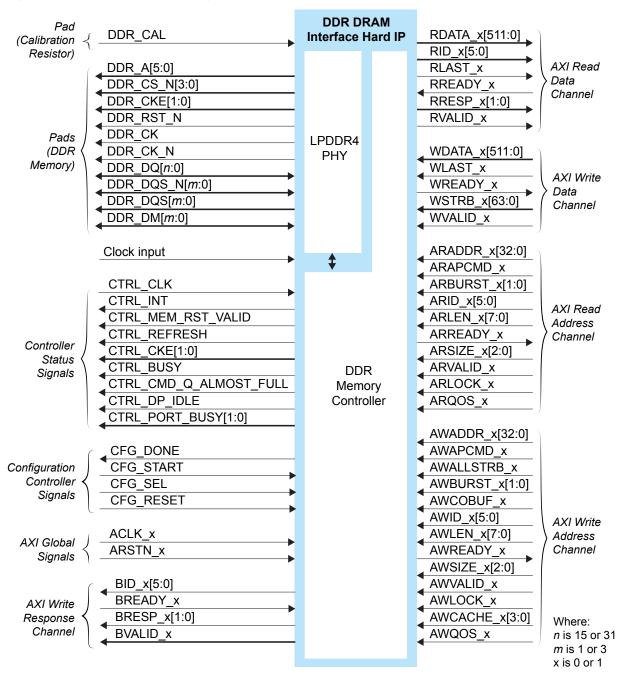

Ti375 FPGAs include a hardened MIPI D-PHY, which you can use with Efinix® MIPI CSI-2 and DSI controller IP cores to create multi-camera, high definition vision systems, edge computing, and hardware acceleration systems. Additionally, these FPGAs have a hardened DDR DRAM controller block that supports LPDDR4 DRAM interfaces.

Together, these features enable a wide variety of applications such as PCIe cards, RF repeaters and radio units, small cell/massive MIMO, cable modems, machine vision, automotive, AV equipment and broadcast, medical imaging, and video bridges.

# **Features**

- High-density, low-power Quantum® compute fabric

- Built on TSMC 16 nm process

- 10-kbit high-speed, embedded SRAM, configurable as single-port RAM, simple dual-port RAM, true dual-port RAM, or ROM

- High-performance DSP blocks for multiplication, addition, subtraction, accumulation, and up to 15-bit variable-right-shifting

- Versatile on-chip clocking

- Low-skew global network supporting 32 clock or control signals

- Regional and local clock networks

- Up to 12 PLLs with support for fractional-N division, programmable duty cycle, spread-spectrum clocking, and dynamic reconfiguration

- FPGA interface blocks

- 32-bit quad-core hardened RISC-V block

- Four high-speed transceiver banks, each with 4 lanes:

- Support data rates from 1.25 Gbps up to 16 Gbps per channel

- PCIe Gen4 x4:

- Compliant with the PCIe® 4.0, 3.0, 2.1, and 1.1 specifications

- Support x1, x2, and x4 configurations

- Configure as Root Port (RP) or End Point (EP)

- Single Root IO Virtualization (SRIOV)

- Supports SGMII and 10GBase-KR protocols as well as PMA Direct

- Two LPDDR4/4x PHY interfaces (supporting x32 DQ widths) with memory controller hard IP

- Three MIPI D-PHY RX and TX interfaces with speeds up to 2.5 Gbps

- Two varieties of general-purpose I/O (GPIO) pins:

- High-voltage I/O (HVIO) pins support 1.8, 2.5, and 3.3 V

- Configurable high-speed I/O (HSIO) pins support

- Single-ended and differential I/O

- LVDS, subLVDS, Mini-LVDS, and RSDS (RX, TX, and bidirectional), up to 1.5 Gbps

- MIPI lane (DSI and CSI) in high-speed and low-power modes, up to 1.5 Gbps

- One oscillator

- Spread-Spectrum Clocking (SSC) PLL

- Flexible device configuration

- Standard SPI interface (active, passive, and daisy chain)

- JTAG interface

- Supports internal reconfiguration

- Single-event upset (SEU) detection feature

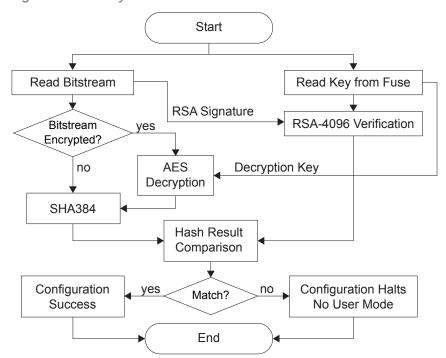

- Optional security feature

- Asymmetric bitstream authentication using RSA-4096

- Bitstream encryption/decryption using AES-GCM

- Fully supported by the Efinity® software, an RTL-to-bitstream compiler

**Important:** All specifications are preliminary and pending hardware characterization.

Table 1: Ti375 FPGA Resources

| Logic<br>Elements | eXchangeable Logic<br>and Routing (XLR) Cells |                     | Global Clock and Control Memory |         | Embedded<br>Memory   | Embedded<br>DSP Blocks |

|-------------------|-----------------------------------------------|---------------------|---------------------------------|---------|----------------------|------------------------|

| (LEs)             | Total                                         | SRL8 <sup>(1)</sup> | Signals                         | (Mbits) | Blocks<br>(10 Kbits) |                        |

| 370,137           | 362,880                                       | 67,200              | Up to 32                        | 27.53   | 2,688                | 1,344                  |

<sup>(1)</sup> Number of XLR that can be configured as shift register with 8 maximum taps.

Table 2: Ti375 Package-Dependent Resources

|                                   | Resource                                                           | N484    | C529 | N1156   |

|-----------------------------------|--------------------------------------------------------------------|---------|------|---------|

| Single-ended GPIO (maximum)       | HVIO<br>LVCMOS: 1.8, 2.5, 3.0, 3.3 V<br>LVTTL: 3.0, 3.3 V          | 20      | 51   | 103     |

|                                   | HSIO (1.2, 1.35, 1.5, 1.8 V LVCMOS, HSTL, and SSTL) <sup>(2)</sup> | 85      | 176  | 234     |

| Differential GPIO                 | HSIO (LVDS, Differential HSTL, and SSTL) <sup>(2)</sup>            | 42      | 88   | 117     |

| (maximum)                         | HSIO (MIPI D-PHY Data Lanes)                                       | 28      | 64   | 100     |

|                                   | HSIO (MIPI D-PHY Clock Lanes)                                      | 7       | 11   | 17      |

| LPDDR4 PHY with memory controller | x32 DQ width                                                       | 1       | 1    | 2       |

| MIPI D-PHY Hard                   | RX                                                                 | 1       | -    | 3       |

| Blocks                            | TX or SSC PLL                                                      | 1       | -    | 3       |

| Global clock or control           | signals from GPIO pins                                             | 17      | 29   | 32      |

| Fractional PLLs                   |                                                                    | 9       | 12   | 12      |

| Transceiver banks                 | PCle                                                               | 1xGen3  | -    | 2xGen4  |

|                                   | SGMII, 10GBase-KR, or PMA Direct                                   | up to 2 | -    | up to 4 |

# Available Package Options

Table 3: Available Packages

| Package         | Dimensions (mm x mm) | Pitch (mm) |

|-----------------|----------------------|------------|

| 484-ball FBGA   | 18 x 18              | 0.8        |

| 529-ball FBGA   | 19 x 19              | 0.8        |

| 1,156-ball FBGA | 35 x 35              | 1.0        |

<sup>(2)</sup> GPIOB\_PN\_00, GPIOB\_PN\_01, and GPIOB\_PN\_02 do not support the SSTL and HSTL input I/O standards.

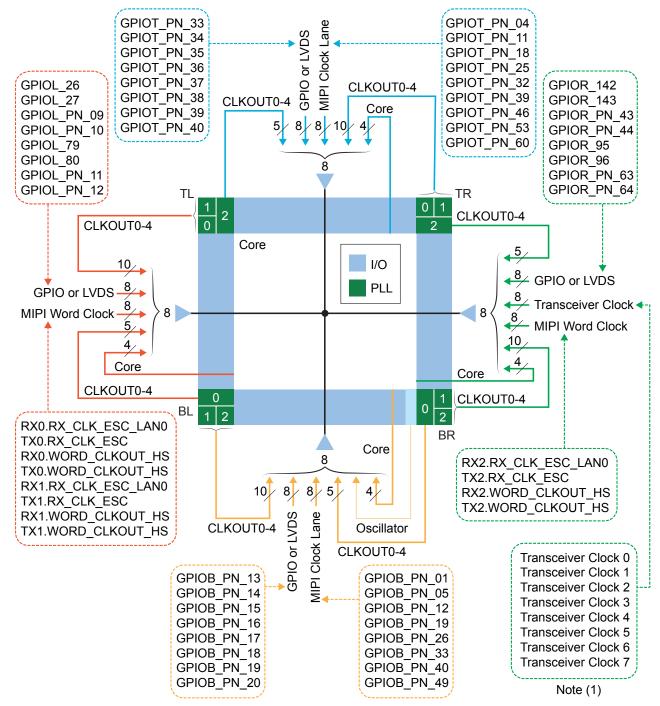

# Device Core Functional Description

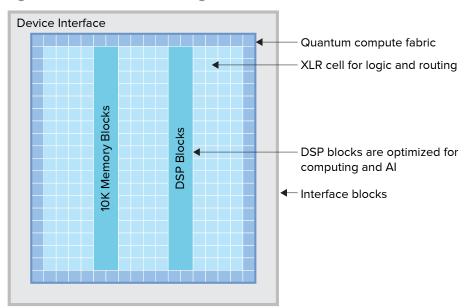

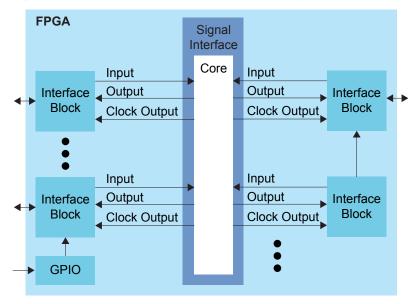

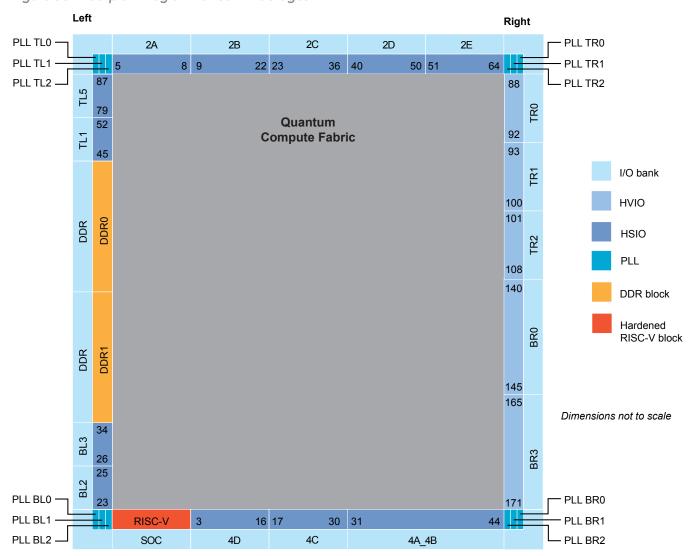

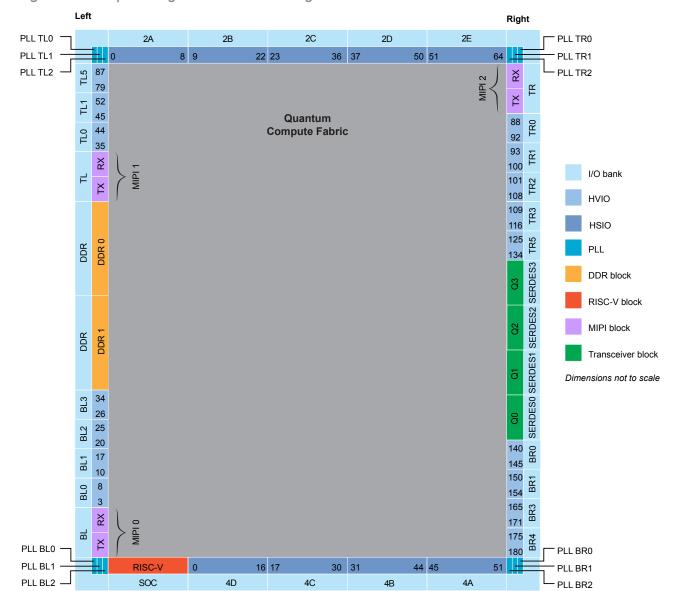

Ti375 FPGAs feature an eXchangeable Logic and Routing (XLR) cell that Efinix® has optimized for a variety of applications. Titanium FPGAs contain LEs that are constructed from XLR cells. Each FPGA in the Titanium family has a custom number of building blocks to fit specific application needs. As shown in the following figure, the FPGA includes I/O ports on all four sides, as well as columns of LEs, memory, and DSP blocks. A control block within the FPGA handles configuration.

Figure 1: Ti375 FPGA Block Diagram

Interface blocks include GPIO, LVDS, PLL, MIPI lane I/O, MIPI D-PHY, DDR DRAM, RISC-V, and transceivers.

### XLR Cell

The eXchangeable Logic and Routing (XLR) cell is the basic building block of the Quantum<sup>®</sup> architecture. The Efinix<sup>®</sup> XLR cell combines logic and routing and supports both functions. This unique innovation greatly enhances the transistor flexibility and utilization rate, thereby reducing transistor counts and silicon area significantly.

**Learn more:** For more detailed on the advantages the XLR cell brings to Titanium FPGAs, read the Why the XLR Cell is a Big Deal White Paper.

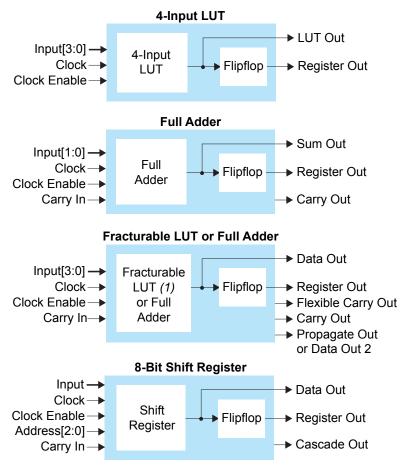

The XLR cell functions as:

- A 4-input LUT that supports any combinational logic function with four inputs.

- A simple full adder.

- An 8-bit shift register that can be cascaded.

- A fracturable LUT or full adder.

The logic cell includes an optional flipflop. You can configure multiple logic cells to implement arithmetic functions such as adders, subtractors, and counters.

Figure 2: Logic Cell Functions

1. The fracturable LUT is a combination of a 3-input LUT and a 2-input LUT. They share 2 of the same inputs.

**Learn more:** Refer to the **Quantum® Titanium Primitives User Guide** for details on the Titanium logic cell primitves.

## **Embedded Memory**

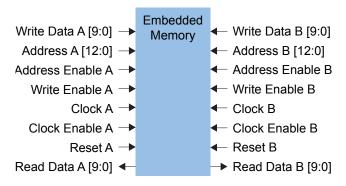

The core has 10-kbit high-speed, synchronous, embedded SRAM memory blocks. Memory blocks can operate as single-port RAM, simple dual-port RAM, true dual-port RAM, or ROM. You can initialize the memory content during configuration. The Efinity® software includes a memory cascading feature to connect multiple blocks automatically to form a larger array. This feature enables you to instantiate deeper or wider memory modules.

Note: The block RAM content is random and undefined if it is not initialized.

The read and write ports support independently configured data widths, an address enable, and an output register reset. The simple dual-port mode also supports a write byte enable.

**Learn more:** Refer to the Quantum<sup>®</sup> Titanium Primitives User Guide for details on the Titanium RAM configuration.

#### True Dual-Port Mode

The memory read and write ports have the following modes for addressing the memory (depth x width):

| 1024 x 8 | 2048 x 4  | 4096 x 2 |

|----------|-----------|----------|

| 8192 x 1 | 1024 x 10 | 2048 x 5 |

Figure 3: RAM Block Diagram (True Dual-Port Mode)

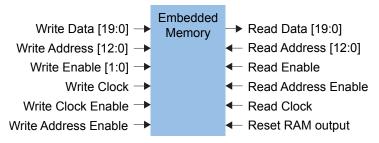

### Simple Dual-Port Mode

The memory read and write ports have the following modes for addressing the memory (depth x width):

| 512 x 16 | 1024 x 8 | 2048 x 4  | 4096 x 2 |

|----------|----------|-----------|----------|

| 8192 x 1 | 512 x 20 | 1024 x 10 | 2048 x 5 |

Figure 4: Simple Dual-Port Mode RAM Block Diagram (512 x 20 Configuration)

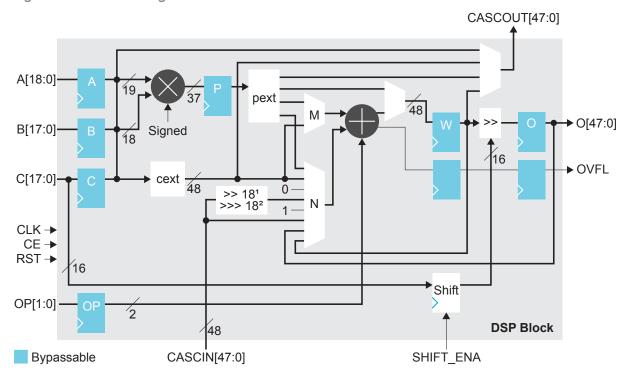

### **DSP Block**

The Titanium FPGA has high-performance, complex DSP blocks that can perform multiplication, addition, subtraction, accumulation, and 4-bit variable right shifting. The 4-bit variable right shift supports one lane in normal mode, two lanes in dual mode and four lanes in quad mode. Each DSP block has four modes, which support the following multiplication operations:

- *Normal*—One 19 x 18 integer multiplication with 48-bit addition/subtraction.

- *Dual*—One 11 x 10 integer multiplication and one 8 x 8 integer multiplication with two 24-bit additions/subtractions.

- *Quad*—One 7 x 6 integer multiplication and three 4 x 4 integer multiplications with four 12-bit additions/subtractions.

**Important:** The 7 x 6 Quad mode output is truncated to 12-bit.

• Float—One fused-multiply-add/subtract/accumulate (FMA) BFLOAT16 multiplication.

The integer multipliers can represent signed or unsigned values based on the SIGNED parameter. When multiple EFX\_DSP12 or EFX\_DSP24 primitives are mapped to the same DSP block, they must have the same SIGNED value. The inputs to the multiplier are the A and B data inputs. Optionally, you can use the result of the multiplier in an addition or subtraction operation.

Figure 5: DSP Block Diagram

- 1. Logical right-shift-by-18.

- 2. Arithmetic right-shift-by-18.

**Learn more:** Refer to the **Quantum® Titanium Primitives User Guide** for details on the Titanium DSP block primitives.

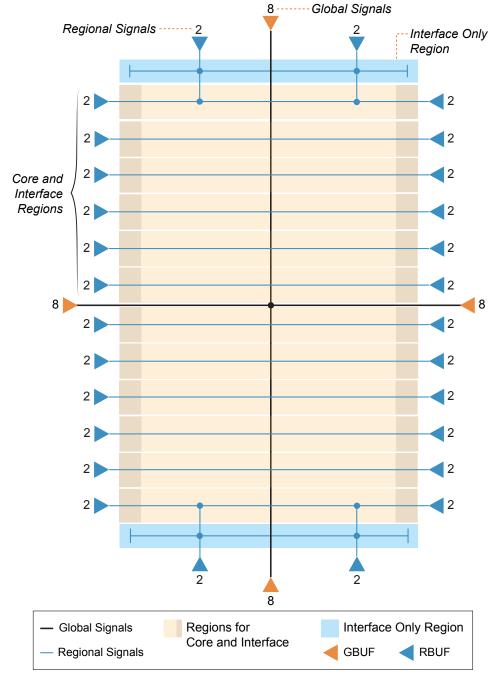

## Clock and Control Network

The clock and control network is distributed through the FPGA to provide clocking for the core's LEs, memory, DSP blocks, I/O blocks, and control signals. The FPGA has 32 global signals that can be used as either clocks or control signals. The global signals are balanced trees that feed the whole FPGA.

The FPGA also has regional signals that can only reach certain FPGA regions, including the top or bottom edges. The FPGA has 12 regional networks for the core, right interface, and left interface blocks. The top and bottom interface blocks have 1 regional clock network each. You can drive the right and left sides of each region independently. Each region also has a local network of clock signals that can only be used in that region.

The core's global buffer (GBUF) blocks drive the global and regional networks. Signals from the core and interface can drive the GBUF blocks.

Each network has dedicated enable logic to save power by disabling the clock tree. The logic dynamically enables/disables the network and guarantees no glitches at the output.

Figure 6: Global and Regional Clock Network Overview

The transceivers drive some of the regional buffers on the right side. See Figure 15 on page 23 for details.

The regional clocks can also drive adjacent regions. See **Driving the Regional Network** on page 21 for details.

### Clock Sources that Drive the Global and Regional Networks

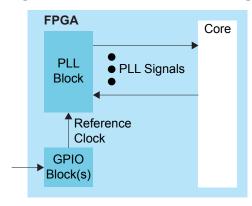

The Titanium global and regional networks are highly flexible and configurable. Clock sources can come from interface blocks, such as GPIO or PLLs, or from the core fabric.

Table 4: Clock Sources that Drive the Global and Regional Networks

| Source                                  | Description                                                                                                                                            |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO                                    | Supports GCLK and RCLK. (Only the P resources support this connection type).                                                                           |

| LVDS RX                                 | Supports GCLK and RCLK.                                                                                                                                |

| MIPI D-PHY RX, TX, and SSC PLL          | Can drive the word clock onto the global and regional clock networks.                                                                                  |

| Transceiver TX, RX, and PIPE P clocks   | Can drive the global and regional clock networks on the right side.                                                                                    |

| MIPI RX Lane (configured as clock lane) | Supports GCLK (default) and RCLK. You can only use resources that are identified as clocks.                                                            |

| PLL                                     | All output clocks connect to the global network.  Refer to Driving the Regional Network on page 21 for the PLL clocks that drive the regional network. |

| Oscillator                              | Connects to global buffer.                                                                                                                             |

| Core                                    | Signals from the core logic can drive the global or regional network.                                                                                  |

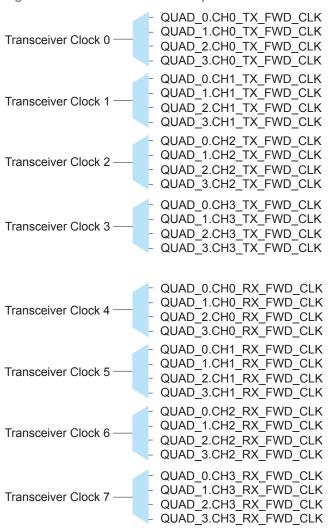

### Driving the Global Network

You can access the global clock network using the global clock GPIO pins, PLL outputs, oscillator output, MIPI word clocks, and core-generated clocks.

A clock multiplexing network controls which interface blocks can drive the global and regional networks. Eight of the clock multiplexers are dynamic (two on each side of the FPGA), allowing you to change which clock drives the global signal in user mode.

**Learn more:** Refer to the **Quantum® Titanium Primitives User Guide** for information on how to configure the global and regional clock networks.

The following figure shows the global network clock sources graphically.

Figure 7: Clock Sources that Drive the Global Network

#### Note:

1. See Figure 8 on page 16 for the transceiver clocks that can drive the global network.

Figure 8: Transceiver Clock Multiplexers

Numerous clock sources feed the global network. These signals are multiplexed together with static and dynamic clock multiplexers.

The dynamic multiplexers are configurable by the user at run-time. You can choose which clock source drives which input to the dynamic multiplexer. When you enable the dynamic multiplexer, you specify a select bus to choose which clock source is active.

When dynamically switching between the clock inputs of a dynamic multiplexer, both the currently active input and the input you intend to switch to must have toggling clocks during the switching period. Additionally, upon configuration completion and when the device transitions into user mode, input 0 of the dynamic multiplexer becomes the default active input. Therefore, you must feed a toggling clock to input 0 before switching to other inputs.

The following figures show the resources that drive each multiplexer.

PLL TL2 CLKOUT3 **GPIO** PLL TR0 CLKOUT3 **MIPI Clock Lane** GPIOT PN 36 **Dynamic Multiplexer** GPIOT PN 40 Static Multiplexer Core Clock 3 PLL TL2 CLKOUT2 PLL TR1 CLKOUT3 PLL TR0 CLKOUT2 PLL TL2 CLKOUT4 **GPIOT PN 35** GPIOT PN 39 Core Clock 2 PLL TR1 CLKOUT2 PLL TR0 CLKOUT4 PLL TL2 CLKOUT0 GPIOT\_PN\_04 PLL TR0 CLKOUT0 GPIOT PN 33 **GPIOT PN 37** PLL TL2 CLKOUT4 **GPIOT PN 18** Core Clock 0 PLL TR0 CLKOUT1 PLL TL2 CLKOUT1 PLL TR1 CLKOUT0 PLL TR0 CLKOUT1 GPIOT\_PN\_11 **GPIOT PN 34** GPIOT PN 38 PLL TL2 CLKOUT3 GPIOT PN 25 Core Clock 1 PLL TR0 CLKOUT2 PLL TR1 CLKOUT1 PLL TR1 CLKOUT4 PLL TL2 CLKOUT3 PLL TL2 CLKOUT0 GPIOT\_PN\_32 PLL TR0 CLKOUT3 GPIOT\_PN\_36 GPIOT\_PN\_40 Core Clock 3 PLL TR1 CLKOUT3 PLL TL2 CLKOUT4 PLL TL2 CLKOUT2 PLL TR0 CLKOUT0 PLL TR0 CLKOUT2 GPIOT\_PN\_39 GPIOT PN 35 GPIOT\_PN\_39 Core Clock 2 PLL TR1 CLKOUT2 - PLL TL2 CLKOUT2 PLL TR0 CLKOUT4 PLL TR0 CLKOUT3 PLL TL2 CLKOUT1 GPIOT\_PN\_04 - GPIOT\_PN\_46 PLL TR0 CLKOUT1 GPIOT\_PN\_34 GPIOT\_PN\_38 Core Clock 1 PLL TR1 CLKOUT1 PLL TL2 CLKOUT1 PLL TR1 CLKOUT4 PLL TR0 CLKOUT4 PLL TL2 CLKOUT0 **GPIOT PN 53** PLL TR0 CLKOUT0 GPIOT\_PN\_33 GPIOT\_PN\_37 Core Clock 0 PLL TR1 CLKOUT0 GPIOT\_PN\_60

Figure 9: Clock Sources that Drive the Multiplexers: Top

**GPIO** PLL BR0 CLKOUT3 **MIPI Clock Lane** PLL BL1 CLKOUT3 GPIOB PN 16 Dynamic Multiplexer GPIOB\_PN\_20 Static Multiplexer Core Clock 3 PLL BR0 CLKOUT2 PLL BL2 CLKOUT3 PLL BL1 CLKOUT2 PLL BR0 CLKOUT4 GPIOB PN 15 GPIOB PN 19 Core Clock 2 PLL BL2 CLKOUT2 PLL BL1 CLKOUT4 PLL BR0 CLKOUT0 PLL BL1 CLKOUT0 GPIOB PN 13 GPIOB PN 17 PLL BR0 CLKOUT4 GPIOB\_PN\_05 Core Clock 0 PLL BL1 CLKOUT1 PLL BR0 CLKOUT1 PLL BL2 CLKOUT0 PLL BL1 CLKOUT1 GPIOB\_PN\_01 GPIOB PN 14 Oscillator GPIOB PN 18 PLL BR0 CLKOUT3 GPIOB\_PN\_12 Core Clock 1 PLL BL1 CLKOUT2 PLL BL2 CLKOUT1 PLL BL2 CLKOUT4 PLL BR0 CLKOUT0 PLL BR0 CLKOUT3 GPIOB\_PN\_19 PLL BL1 CLKOUT3 GPIOB PN 16 GPIOB PN 20 Core Clock 3 PLL BL2 CLKOUT3 PLL BR0 CLKOUT4 PLL BR0 CLKOUT2 PLL BL1 CLKOUT0 GPIOB\_PN\_26 PLL BL1 CLKOUT2 GPIOB PN 15 GPIOB\_PN\_19 Core Clock 2 PLL BL2 CLKOUT2 PLL BR0 CLKOUT2 PLL BL1 CLKOUT4 PLL BL1 CLKOUT3 PLL BR0 CLKOUT1 - GPIOB\_PN\_33 PLL BL1 CLKOUT1 GPIOB PN 14 GPIOB\_PN\_18 Core Clock 1 PLL BL2 CLKOUT1 PLL BR0 CLKOUT1 PLL BL2 CLKOUT4 PLL BR0 CLKOUT0 PLL BL1 CLKOUT4 PLL BL1 CLKOUT0 GPIOB\_PN\_40 GPIOB PN 13 GPIOB PN 17 Core Clock 0 PLL BL2 CLKOUT0 GPIOB\_PN\_49 Oscillator

Figure 10: Clock Sources that Drive the Multiplexers: Bottom

PLL BL0 CLKOUT3 PLL TL0 CLKOUT3 Dynamic Multiplexer GPIOL PN 10 Static Multiplexer GPIOL\_PN\_12 Core Clock 3 PLL BL0 CLKOUT2 PLL TL1 CLKOUT3 PLL TL0 CLKOUT2 PLL BL0 CLKOUT4 GPIOL PN 09 GPIOL\_PN\_11 Core Clock 2 PLL TL1 CLKOUT2 PLL TL0 CLKOUT4 PLL BL0 CLKOUT0 PLL TL0 CLKOUT0 GPIOL PN 26 GPIOL PN 79 PLL BL0 CLKOUT4 MIPI TX0 RX\_CLK ESC Core Clock 0 PLL TL0 CLKOUT1 PLL TL1 CLKOUT0 PLL BL0 CLKOUT1 PLL TL0 CLKOUT1 MIPI RX0 GPIOL\_PN\_27 RX CLK ESC LAN0 GPIOL\_PN\_80 PLL BL0 CLKOUT3 MIPI RX0 WORD CLKOUT HS Core Clock 1 PLL TL0 CLKOUT2 PLL TL1 CLKOUT1 PLL TL1 CLKOUT4 - PLL BL0 CLKOUT0 PLL BL0 CLKOUT3 - MIPI TX0 WORD CLKOUT HS PLL TL0 CLKOUT3 GPIOL PN 10 GPIOL PN 12 Core Clock 3 PLL TL1 CLKOUT3 PLL BL0 CLKOUT4 PLL BL0 CLKOUT2 PLL TL0 CLKOUT0 PLL TL0 CLKOUT2 MIPI RX1 RX CLK ESC LAN0 GPIOL PN 09 GPIOL PN 11 Core Clock 2 PLL TL1 CLKOUT2 PLL BL0 CLKOUT2 PLL TL0 CLKOUT4 PLL TL0 CLKOUT3 PLL BL0 CLKOUT1 MIPI TX1 RX\_CLK\_ESC PLL TL0 CLKOUT1 GPIOL PN 27 GPIOL PN 80 Core Clock 1 PLL TL1 CLKOUT1 PLL BL0 CLKOUT1 PLL TL1 CLKOUT4 PLL BL0 CLKOUT0 PLL TL0 CLKOUT4 MIPI RX1 WORD CLKOUT HS PLL TL0 CLKOUT0 GPIOL\_PN\_26 GPIOL PN 79 Core Clock 0 PLL TL1 CLKOUT0 MIPI TX1 WORD CLKOUT HS

Figure 11: Clock Sources that Drive the Multiplexers: Left

PLL TR2 CLKOUT3 Dynamic Multiplexer PLL BR1 CLKOUT3 GPIOR PN 44 Static Multiplexer GPIOR\_PN\_64 PLL TR2 CLKOUT2 Core Clock 3 PLL BR1 CLKOUT2 PLL BR2 CLKOUT3 GPIOR PN 43 PLL TR2 CLKOUT4 GPIOR PN 63 MIPI TX2 Core Clock 2 RX CLK ESC PLL BR2 CLKOUT2 PLL BR1 CLKOUT4 MIPI RX2 PLL TR2 CLKOUT0 RX\_CLK\_ESC\_LAN0 PLL BR1 CLKOUT0 GPIOR PN 142 GPIOR\_PN\_95 PLL TR2 CLKOUT4 Transceiver Clock 1 (1) Core Clock 0 PLL BR1 CLKOUT1 PLL TR2 CLKOUT1 PLL BR2 CLKOUT0 PLL BR1 CLKOUT1 Transceiver Clock 0 (1) GPIOR PN 143 MIPI RX2 PLL TR2 CLKOUT3 GPIOR\_PN\_96 WORD\_CLKOUT\_HS Transceiver Clock 2 (1) Core Clock 1 PLL BR1 CLKOUT2 PLL BR2 CLKOUT1 PLL BR2 CLKOUT4 MIPI TX2 PLL TR2 CLKOUT3 PLL TR2 CLKOUT0 WORD\_CLKOUT\_HS Transceiver Clock 3 (1) PLL BR1 CLKOUT3 GPIOR PN 44 GPIOR\_PN\_64 PLL BR1 CLKOUT0 PLL TR2 CLKOUT2 Core Clock 3 Transceiver Clock 4 (1) PLL BR1 CLKOUT2 PLL BR2 CLKOUT3 GPIOR PN 43 PLL TR2 CLKOUT4 GPIOR\_PN\_63 MIPI TX2 RX CLK ESC Core Clock 2 PLL BR2 CLKOUT2 PLL BR1 CLKOUT4 PLL TR2 CLKOUT2 MIPI RX2 PLL BR1 CLKOUT3 PLL TR2 CLKOUT1 RX\_CLK\_ESC\_LAN0 Transceiver Clock 5 (1) PLL BR1 CLKOUT1 GPIOR PN 143 GPIOR\_PN\_96 Core Clock 1 PLL TR2 CLKOUT1 PLL BR2 CLKOUT1 PLL TR2 CLKOUT0 PLL BR1 CLKOUT4 PLL BR1 CLKOUT0 PLL BR2 CLKOUT4 Transceiver Clock 6 (1) GPIOR PN 142 MIPI TX2 GPIOR\_PN\_95 WORD CLKOUT HS Core Clock 0 PLL BR2 CLKOUT0 Transceiver Clock 7 (1) MIPI RX2 WORD CLKOUT HS

Figure 12: Clock Sources that Drive the Multiplexers: Right

Note:

See Figure 8 on page 16 for the transceiver clocks that can drive the global network.

### Driving the Regional Network

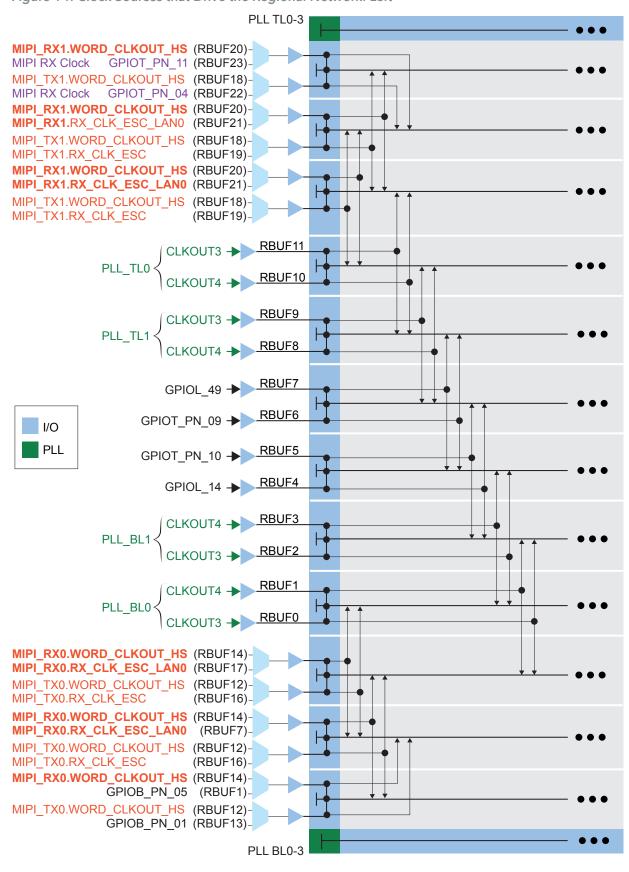

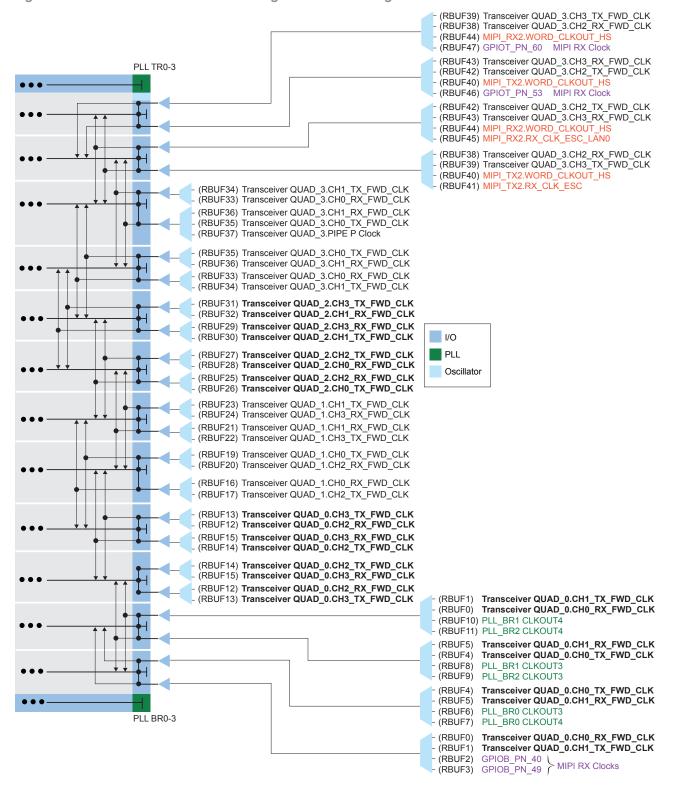

The following figures show the regional network clock sources graphically.

GPIOT\_PN\_32 (RBUF3)-(RBUF4) GPIOT\_PN\_39 GPIOT\_PN\_25 (RBUF2)-(RBUF5) GPIOT\_PN\_46 MIPI RX MIPI RX Clocks GPIOT\_PN\_18 (RBUF1)-Clocks (RBUF6) GPIOT\_PN\_53 GPIOT\_PN\_11 (RBUF23)-(RBUF7) GPIOT\_PN\_60 PLL TL0-3 PLL TR0-3 I/O PLL Oscillator PLL BL0-3 PLL BR0-3 GPIOB\_PN\_01 (RBUF0) -(RBUF6) GPIOB PN 40 GPIOB\_PN\_05 (RBUF1)\_ (RBUF5) GPIOB\_PN\_33 MIPI RX GPIOB PN 05 (RBUF1) -Clocks (RBUF4) GPIOB\_PN\_26

Figure 13: Clock Sources that Drive the Regional Network: Top and Bottom

GPIOB\_PN\_12 (RBUF2)\_

(RBUF3) GPIOB\_PN\_19

Figure 14: Clock Sources that Drive the Regional Network: Left

Figure 15: Clock Sources that Drive the Regional Network: Right

#### Driving the Local Network

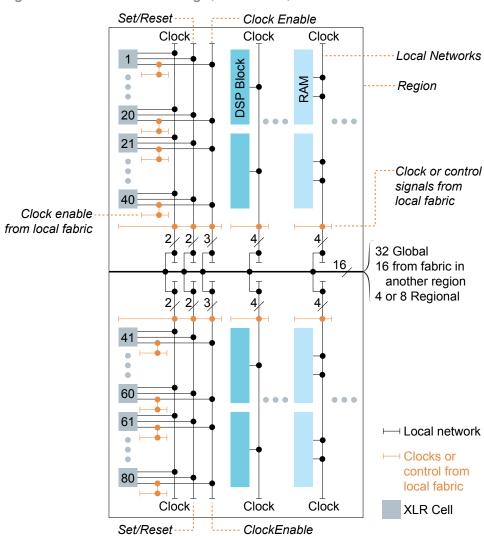

As described previously, the FPGA has horizontal clock regions. The top and bottom regions are **only** for the top and bottom interfaces. The other regions are for the core logic (XLR cells, DSP Blocks, and RAM) and the interfaces on the sides.

#### Local Network for Core Logic

As shown in the following figure, the regions that contain the core logic are 80 XLR cells tall, and the local network connects an area that is 40 XLR cells tall. Additionally, each column has it's own local network. For example, in the first column, XLR cells 1 - 40 are in the same local network and XLR cells 41 - 80 are in another local network. DSP Blocks and RAM also have their own local networks. This pattern of block/local network is repeated for each column in the die.

Figure 16: Clock Sources for Logic, DSP Blocks, and RAM

There are 16 signals that can feed the local networks. These signals can come from several sources:

- The global network (32 possible signals)

- The core fabric in another region (16 possible signals)

- The regional network (12 possible signals)

Additionally, the local fabric can generate clock and control signals for the local network. The fabric can also drive the clock enable for the XLR cell directly, allowing each XLR cell to have a unique clock enable.

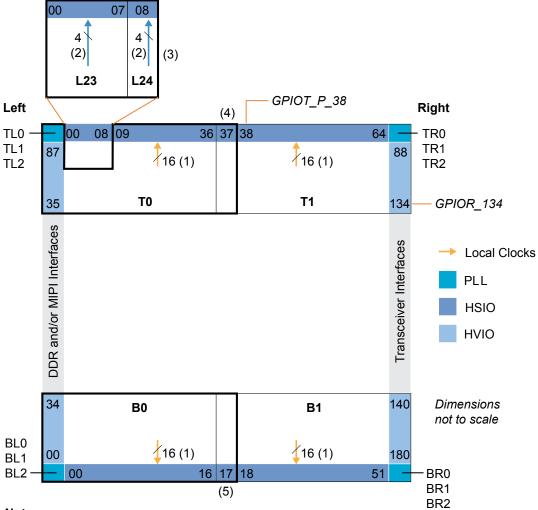

#### Local Network for Interface Regions

The following figure shows the local clock networks for the interface blocks. There are a limited number of unique clocks per local clock region.

- The top and bottom regions can each support up to 16 unique clock signals; 14 from the global network and 2 from the fabric.

- The left and right regions can each support up to 4 unique clock signals. Up to 2 can come from the routing fabric, the rest come from the global or regional buffers. These regions are the same height as the core local regions (that is, 40 rows).

Figure 17: Clock Sources that Drive the Interfaces

#### Notes:

- 1. 14 signals come from the global network; 2 come from the routing fabric.

- 2. Up to 2 signals can come from the routing fabric. The rest come from the regional/global buffer.

- 3. GPIOT\_PN\_00 07 are in region L23. GPIOT\_PN\_08 is in regions L23 and L24.

- 4. GPIOT\_PN\_37 is in regions T0 and T1.

- 5. GPIOB\_PN\_17 is in regions B0 and B1.

# Device Interface Functional Description

The device interface wraps the core and routes signals between the core and the device I/O pads through a signal interface. Because they use the flexible Quantum® architecture, devices in the Titanium family support a variety of interfaces to meet the needs of different applications.

**Learn more:** The following sections describe the available device interface features in Ti375 FPGAs. Refer to the **Titanium Interfaces User Guide** for details on the Efinity<sup>®</sup> Interface Designer settings.

## Interface Block Connectivity

The FPGA core fabric connects to the interface blocks through a signal interface. The interface blocks then connect to the package pins. The core connects to the interface blocks using three types of signals:

- *Input*—Input data or clock to the FPGA core

- Output—Output from the FPGA core

- Clock output—Clock signal from the core clock tree

Figure 18: Interface Block and Core Connectivity

GPIO blocks are a special case because they can operate in several modes. For example, in alternate mode the GPIO signal can bypass the signal interface and directly feed another interface block. So a GPIO configured as an alternate input can be used as a PLL reference clock without going through the signal interface to the core.

When designing for Titanium FPGAs, you create an RTL design for the core and also configure the interface blocks. From the perspective of the core, outputs from the core are inputs to the interface block and inputs to the core are outputs from the interface block.

The Efinity netlist always shows signals from the perspective of the core, so some signals do not appear in the netlist:

• GPIO used as reference clocks are not present in the RTL design, they are only visible in the interface block configuration of the Efinity® Interface Designer.

• The FPGA clock tree is connected to the interface blocks directly. Therefore, clock outputs from the core to the interface are not present in the RTL design, they are only part of the interface configuration (this includes GPIO configured as output clocks).

The following sections describe the different types of interface blocks. Signals and block diagrams are shown from the perspective of the interface, not the core.

#### **GPIO**

The Ti375 FPGA supports two types of GPIO:

- High-voltage I/O (HVIO)—Simple I/O blocks that can support single-ended I/O standards.

- *High-speed I/O (HSIO)*—Complex I/O blocks that can support single-ended and differential I/O functionality.

The I/O logic comprises three register types:

- Input—Capture interface signals from the I/O before being transferred to the core logic

- Output—Register signals from the core logic before being transferred to the I/O buffers

- Output enable—Enable and disable the I/O buffers when I/O used as output

The HVIO supports the following I/O standards.

**Table 5: HVIO Supported Standards**

| Standard     | VCCIO33 (V) | When Configured As |

|--------------|-------------|--------------------|

| LVTTL 3.3 V  | 3.3         | GPIO               |

| LVTTL 3.0 V  | 3.0         | GPIO               |

| LVCMOS 3.3 V | 3.3         | GPIO               |

| LVCMOS 3.0 V | 3.0         | GPIO               |

| LVCMOS 2.5 V | 2.5         | GPIO               |

| LVCMOS 1.8 V | 1.8         | GPIO               |

**Important:** Efinix recommends that you limit the number of 3.0/3.3 V HVIO and 2.5 V HVIO as bidirectional or output to 6 per bank to avoid switching noise. The Efinity® software issues a warning if you exceed the recommended limit.

The HSIO supports the following I/O standards.

Table 6: HSIO Supported I/O Standards

| Standard                                                     | VCCIO (V) |                         | VCCAUX (V) | VREF (V) | When          |

|--------------------------------------------------------------|-----------|-------------------------|------------|----------|---------------|

|                                                              | TX        | RX                      |            |          | Configured As |

| LVCMOS 1.8 V                                                 | 1.8       | 1.8                     | 1.8        | -        | GPIO          |

| LVCMOS 1.5 V                                                 | 1.5       | 1.5                     | 1.8        | -        | GPIO          |

| LVCMOS 1.2 V                                                 | 1.2       | 1.2                     | 1.8        | -        | GPIO          |

| HSTL/Differential HSTL 1.8 V<br>SSTL/Differential SSTL 1.8 V | 1.8       | 1.8                     | 1.8        | 0.9      | GPIO          |

| HSTL/Differential HSTL 1.5 V<br>SSTL/Differential SSTL 1.5 V | 1.5       | 1.5, 1.8 <sup>(3)</sup> | 1.8        | 0.75     | GPIO          |

<sup>(3)</sup> To prevent pin leakage, you must ensure that the voltage at the pin does not exceed VCCIO.

| Standard                                                     | VCCIO (V) |                                    | VCCAUX (V) | VREF (V) | When          |

|--------------------------------------------------------------|-----------|------------------------------------|------------|----------|---------------|

|                                                              | TX        | RX                                 |            |          | Configured As |

| SSTL/Differential SSTL 1.35 V                                | 1.35      | 1.35, 1.5, 1.8 <sup>(3)</sup>      | 1.8        | 0.675    | GPIO          |

| HSTL/Differential HSTL 1.2 V<br>SSTL/Differential SSTL 1.2 V | 1.2       | 1.2, 1.35, 1.5, 1.8 <sup>(3)</sup> | 1.8        | 0.6      | GPIO          |

| LVDS/RSDS/mini-LVDS                                          | 1.8       | 1.5, 1.8 <sup>(3)</sup>            | 1.8        | -        | LVDS          |

| Sub-LVDS                                                     | 1.8       | 1.5, 1.8 <sup>(3)</sup>            | 1.8        | -        | LVDS          |

| MIPI                                                         | 1.2       | 1.2                                | 1.8        | -        | MIPI Lane     |

| SLVS                                                         | 1.2       | 1.2                                | 1.8        | -        | LVDS          |

The differential receivers are powered by VCCAUX, which gives you the flexibility to choose the VCCIO you want to use. However, you must comply to the requirements stated in the previous table.

## Features for HVIO and HSIO Configured as GPIO

The following table describes the features for HVIO and HSIO configured as GPIO.

Table 7: Features for HVIO and HSIO Configured as GPIO

| Feature                                           | HVIO | HSIO<br>Configured<br>as GPIO |

|---------------------------------------------------|------|-------------------------------|

| Double-data I/O (DDIO)                            | ~    | ~                             |

| Dynamic pull-up                                   | -    | <b>✓</b>                      |

| Pull-up/Pull-down                                 | ~    | ~                             |

| Slew-Rate Control                                 | -    | <b>✓</b>                      |

| Variable Drive Strength                           | ~    | ~                             |

| Schmitt Trigger                                   | ~    | ~                             |

| 1:4 Serializer/Deserializer (Full rate mode only) | -    | ~                             |

| Programmable Bus Hold                             | -    | ~                             |

| Static Programmable Delay Chains                  | ~    | ~                             |

| Dynamic Programmable Delay Chains                 | -    | <b>✓</b>                      |

**Table 8: GPIO Modes**

| GPIO Mode     | Description                                                                                                                                                                                                                                                                                                               |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input         | Only the input path is enabled; optionally registered. If registered, the input path uses the input clock to control the registers (positively or negatively triggered).                                                                                                                                                  |

|               | Select the alternate input path to drive the alternate function of the GPIO. The alternate path cannot be registered.                                                                                                                                                                                                     |

|               | In DDIO mode, two registers sample the data on the positive and negative edges of the input clock, creating two data streams.                                                                                                                                                                                             |

| Output        | Only the output path is enabled; optionally registered. If registered, the output path uses the output clock to control the registers (positively or negatively triggered).                                                                                                                                               |

|               | The output register can be inverted.                                                                                                                                                                                                                                                                                      |

|               | In DDIO mode, two registers capture the data on the positive and negative edges of the output clock, multiplexing them into one data stream.                                                                                                                                                                              |

| Bidirectional | The input, output, and OE paths are enabled; optionally registered. If registered, the input clock controls the input register, the output clock controls the output and OE registers. All registers can be positively or negatively triggered. Additionally, the input and output paths can be registered independently. |

|               | The output register can be inverted.                                                                                                                                                                                                                                                                                      |

| Clock output  | Clock output path is enabled.                                                                                                                                                                                                                                                                                             |

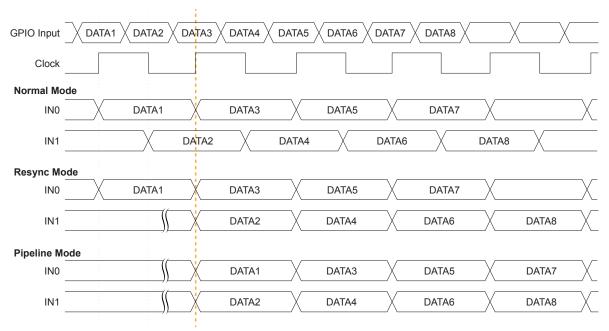

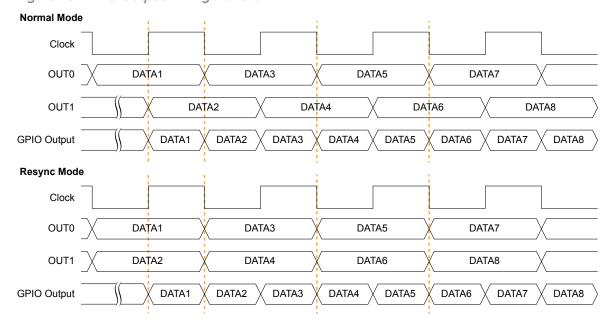

#### Double-Data I/O

Ti375 FPGAs support double data I/O (DDIO) on input and output registers. In this mode, the DDIO register captures data on both positive and negative clock edges. The core receives 2 bit wide data from the interface.

In normal mode, the interface receives or sends data directly to or from the core on the positive and negative clock edges. In resync and pipeline mode, the interface resynchronizes the data to pass both signals on the positive clock edge only.

Figure 19: DDIO Input Timing Waveform

In resync mode, the IN1 data captured on the falling clock edge is delayed one half clock cycle. In the Interface Designer, IN0 is the HI pin name and IN1 is the LO pin name.

Figure 20: DDIO Output Timing Waveform

In the Interface Designer, OUT0 is the HI pin name and OUT1 is the LO pin name.

#### **Programmable Delay Chains**

The HVIO and HSIO configured as GPIO support programmable delay chain. In some cases you can use static and dynamic delays at the same time.

Table 9: Programmable Delay Support

| GPIO Type         | Delay Steps       |                   |

|-------------------|-------------------|-------------------|

|                   | Static Delay      | Dynamic Delay     |

| Single-Ended      |                   |                   |

| HVIO input        | 16                | N/A               |

| HVIO output       | 16                | N/A               |

| HSIO P pin input  | 16                | 64                |

| HSIO P pin output | 16                | N/A               |

| HSIO N pin input  | 16                | N/A               |

| HSIO N pin output | 16                | N/A               |

| Differential      |                   |                   |

| HSIO TX           | 64                | N/A               |

| HSIO RX           | 64 <sup>(4)</sup> | 64 <sup>(4)</sup> |

**Learn more:** Refer to the following tables for the delay step size:

Table 92: Single-Ended I/O Programmable Delay Chain Step Size: Static on page 99

Table 93: Single-Ended I/O Programmable Delay Chain Step Size: Dynamic on page 99

Table 94: Differential I/O Programmable Delay Chain Step Size: Static and Dynamic on page 99

<sup>(4)</sup> You cannot use the static delay and dynamic delay simultaneously.

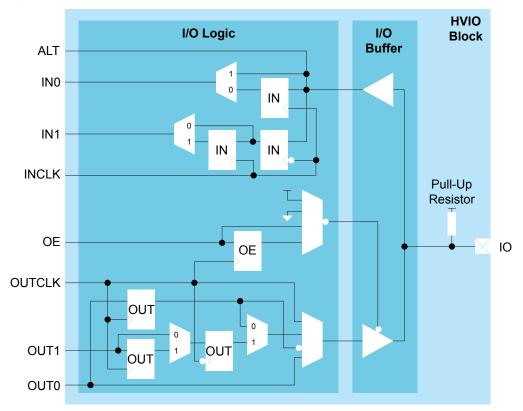

#### HVIO

The HVIOs are grouped into banks. Each bank has its own VCCIO33 that sets the bank voltage for the I/O standard. Each HVIO consists of I/O logic and an I/O buffer. I/O logic connects the core logic to the I/O buffers. I/O buffers are located at the periphery of the device.

Figure 21: HVIO Interface Block

Table 10: HVIO Signals (Interface to FPGA Fabric)

| Signal   | Direction | Description                                                                                                                                                                                                                                                                                         |

|----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN[1:0]  | Output    | Input data from the HVIO pad to the core fabric.  IN0 is the normal input to the core. In DDIO mode, IN0 is the data captured on the positive clock edge (HI pin name in the Interface Designer) and IN1 is the data captured on the negative clock edge (LO pin name in the Interface Designer).   |

| ALT      | Output    | Alternative input connection (in the Interface Designer, <b>Register Option</b> is <b>none</b> ). HVIO only support pll_clkin as the alternative connection.                                                                                                                                        |

| OUT[1:0] | Input     | Output data to HVIO pad from the core fabric. OUT0 is the normal output from the core. In DDIO mode, OUT0 is the data captured on the positive clock edge (HI pin name in the Interface Designer) and OUT1 is the data captured on the negative clock edge (LO pin name in the Interface Designer). |

| OE       | Input     | Output enable from core fabric to the I/O block. Can be registered.                                                                                                                                                                                                                                 |

| OUTCLK   | Input     | Core clock that controls the output and OE registers. This clock is not visible in the user netlist.                                                                                                                                                                                                |

| INCLK    | Input     | Core clock that controls the input registers. This clock is not visible in the user netlist.                                                                                                                                                                                                        |

Table 11: HVIO Pads

| Signal | Direction     | Description |

|--------|---------------|-------------|

| Ю      | Bidirectional | HVIO pad.   |

#### **HSIO**

Each HSIO block uses a pair of I/O pins as one of the following:

- Single-ended HSIO—Two single-ended I/O pins (LVCMOS, SSTL, HSTL)

- Differential HSIO—One differential I/O pins:

- Differential SSTL and HSTL

- LVDS-Receiver (RX), transmitter (TX), or bidirectional (RX/TX)

- MIPI lane I/O—Receiver (RX) or transmitter (TX)

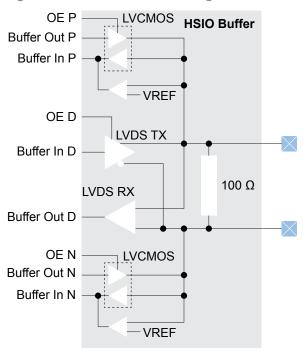

Figure 22: HSIO Buffer Block Diagram

**Important:** When you are using an HSIO pin as a GPIO, make sure to leave at least 1 pair of unassigned HSIO pins between any GPIO and LVDS or MIPI lane pins. This rule applies for pins on each side of the device (top, bottom, left, right). This separation reduces noise. The Efinity software issues an error if you do not leave this separation.

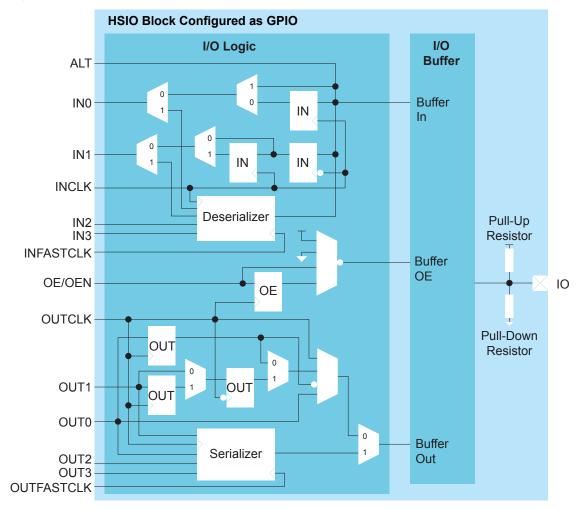

#### **HSIO Configured as GPIO**

You can configure each HSIO block as two GPIO (single-ended) or one GPIO (differential).

Figure 23: I/O Interface Block

Table 12: HSIO Block Configured as GPIO Signals (Interface to FPGA Fabric)

| Signal     | Direction | Description                                                                                                                                                                                                                                           |

|------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN[3:0]    | Output    | Input data from the pad to the core fabric.                                                                                                                                                                                                           |

|            |           | INO is the normal input to the core. In DDIO mode, INO is the data captured on the positive clock edge (HI pin name in the Interface Designer) and IN1 is the data captured on the negative clock edge (LO pin name in the Interface Designer).       |

|            |           | When using the deserializer, the first bit is on INO and the last bit is on IN3.                                                                                                                                                                      |

| ALT        | Output    | Alternative input connection for GCLK, PLL_CLKIN, RCLK, PLL_EXTFB, and VREF.                                                                                                                                                                          |

|            |           | (In the Interface Designer, <b>Register Option</b> is <b>none</b> ).                                                                                                                                                                                  |

| OUT[3:0]   | Input     | Output data to GPIO pad from the core fabric.                                                                                                                                                                                                         |

|            |           | OUT0 is the normal output from the core. In DDIO mode, OUT0 is the data captured on the positive clock edge (HI pin name in the Interface Designer) and OUT1 is the data captured on the negative clock edge (LO pin name in the Interface Designer). |

|            |           | When using the serializer, the first bit is on OUT0 and the last bit is on OUT3.                                                                                                                                                                      |

| OE/OEN     | Input     | Output enable from core fabric to the I/O block. Can be registered. OEN is used in differential mode. Drive it with the same signal as OE.                                                                                                            |

| DLY_ENA    | Input     | (Optional) Enable the dynamic delay control.                                                                                                                                                                                                          |

| DLY_INC    | Input     | (Optional) Dynamic delay control. When DLY_ENA = 1, 1: Increments                                                                                                                                                                                     |

|            |           | 0: Decrements                                                                                                                                                                                                                                         |

|            |           | The updated delay count takes effect approximately 5 ns after the rising edge of the clock.                                                                                                                                                           |

| DLY_RST    | Input     | (Optional) Reset the delay counter.                                                                                                                                                                                                                   |

| OUTCLK     | Input     | Core clock that controls the output and OE registers. This clock is not visible in the user netlist.                                                                                                                                                  |

| OUTFASTCLK | Input     | Core clock that controls the output serializer.                                                                                                                                                                                                       |

| INCLK      | Input     | Core clock that controls the input registers. This clock is not visible in the user netlist.                                                                                                                                                          |

| INFASTCLK  | Input     | Core clock that controls the input serializer.                                                                                                                                                                                                        |

Table 13: GPIO Pads

| Signal       | Direction     | Description |

|--------------|---------------|-------------|

| IO (P and N) | Bidirectional | GPIO pad.   |

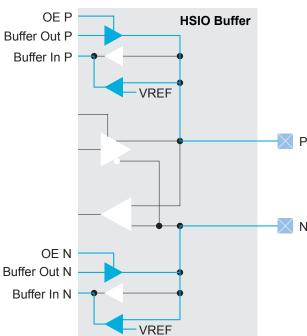

The signal path from the pad through the I/O buffer changes depending on the I/O standard you are using. The following figures show the paths for the supported standards. The blue highlight indicates the path.

OE P

Buffer Out P

Buffer In P

VREF

OE N

Buffer Out N

Buffer In N

Figure 24: I/O Buffer Path for LVCMOS

When using an HSIO with the HSTL or SSTL I/O standards, you must configure an I/O pad of the standard's input path as a VREF pin. There is one programmable VREF per I/O bank.

(!)

**Important:** When configuring an I/O pad of the standard's input path as a VREF pin, you must use the VREF from the same physical I/O bank even when the I/O banks are merged to share a common VCCIO pin.

For I/O banks that do not have the  $\protect\operatorname{VREF}$  pin bonded out, the banks' GPIO pins do not support the HSTL and SSTL input I/O standards.

Figure 25: I/O Buffer Path for HSTL and SSTL

When using an HSIO with the differential HSTL or differential SSTL standard, you must use both GPIO resources in the HSIO. You use the core interface pins associated with the P resource.

OE P

Buffer Out P

VREF

P

OEN P

Buffer Out P

VREF

Figure 26: I/O Buffer Path for Differential HSTL and SSTL

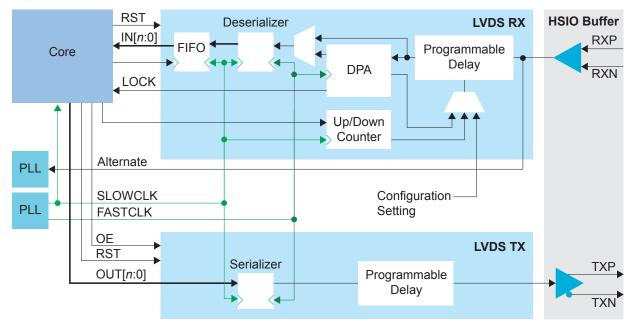

## **HSIO Configured as LVDS**

You can configure each HSIO block in RX, TX, or bidirectional LVDS mode. As LVDS, the HSIO has these features:

- $\bullet$   $\;$  Programmable  $V_{\mathrm{OD}},$  depending on the I/O standard used.

- Programmable pre-emphasis.

- Up to 1.5 Gbps.

- Programmable 100  $\Omega$  termination to save power (you can enable or disable it at runtime).

- LVDS input enable to dynamically enable/disable the LVDS input.

- Support for full rate or half rate serialization.

- Up to 10-bit serialization to support protocols such as 8b10b encoding.

- Programmable delay chains.

- Optional 8-word FIFO for crossing from the parallel (slow) clock to the user's core clock to help close timing (RX only).

- Dynamic phase alignment (DPA) that automatically eliminates skew for clock to data channels and data to data channels by adjusting a delay chain setting so that data is sampled at the center of the bit period. The DPA supports full-rate serialization mode only.

Table 14: Full and Half Rate Serialization

| Mode            | Description                                                                                                                     | Example                                                                                                                                            |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Full rate clock | In full rate mode, the fast clock runs at<br>the same frequency as the data and<br>captures data on the positive clock<br>edge. | Data rate: 800 Mbps Serialization/Deserialization factor: 8 Slow clock frequency: 100 Mhz (800 Mbps / 8) Fast clock frequency: 800 Mhz             |

| Half rate clock | In half rate mode, the fast clock runs at half the speed of the data and captures data on both clock edges.                     | Data rate: 800 Mbps Serialization / Deserialization factor: 8 Slow clock frequency: 100 Mhz (800 Mbps / 8) Fast clock frequency: 400 Mhz (800 / 2) |

You use a PLL to generate the serial (fast) and parallel (slow) clocks for the LVDS pins. The slow clock runs at the data rate divided by the serialization factor.

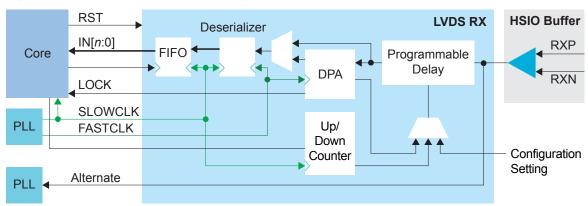

#### LVDS RX

You can configure an HSIO block as one LVDS RX signal.

Figure 27: LVDS RX Interface Block Diagram

Table 15: LVDS RX Signals (Interface to FPGA Fabric)

| Signal     | Direction | Clock Domain       | Description                                                                                                                                                                                                     |

|------------|-----------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN[9:0]    | Output    | SLOWCLK            | Parallel input data to the core. The width is programmable.                                                                                                                                                     |

| ALT        | Output    |                    | Alternate input, only available for an LVDS RX resource in bypass mode (deserialization width is 1; alternate connection type). Alternate connections are PLL_CLKIN, PLL_EXTFB, GCLK, and RCLK.                 |

| SLOWCLK    | Input     | -                  | Parallel (slow) clock.                                                                                                                                                                                          |

| FASTCLK    | Input     | -                  | Serial (fast) clock.                                                                                                                                                                                            |

| FIFO_EMPTY | Output    | FIFOCLK            | This signal is required when you turn on the <b>Enable Clock Crossing FIFO</b> option Indicates that the FIFO is empty.                                                                                         |

| FIFOCLK    | Input     | -                  | This signal is required when you turn on the <b>Enable Clock Crossing FIFO</b> option. Core clock to read from the FIFO.                                                                                        |

| FIFO_RD    | Input     | FIFOCLK            | This signal is required when you turn on the <b>Enable Clock Crossing FIFO</b> option. Enables FIFO to read.                                                                                                    |

| RST        | Input     | FIFOCLK<br>SLOWCLK | (Optional) This signal is available when deserialization is enabled.<br>Asynchronous. Resets the FIFO and deserializer. If the FIFO is enabled, it is relative to FIFOCLK; otherwise it is relative to SLOWCLK. |

| ENA        | Input     | -                  | Dynamically enable or disable the LVDS input buffer. Can save power when disabled.  1: Enabled 0: Disabled                                                                                                      |

| TERM       | Input     | -                  | The signal is available when dynamic termination is enabled. Enables or disables termination in dynamic termination mode.  1: Enabled  0: Disabled                                                              |

| LOCK       | Output    |                    | (Optional) This signal is available when you set <b>Delay Mode</b> to <b>dpa</b> . Indicates that the DPA has achieved training lock and data can be passed.                                                    |

| DLY_ENA    | Input     | SLOWCLK            | This signal is required when you set <b>Delay Mode</b> to <b>dynamic</b> or <b>dpa</b> . Enable the dynamic delay control or the DPA circuit, depending on the LVDS RX delay settings.                          |

| DLY_INC    | Input     | SLOWCLK            | This signal is required when you set <b>Delay Mode</b> to <b>dynamic</b> . Dynamic delay control. Cannot be used with DPA enabled. When DLY_ENA is 1: 1: Increments  0: Decrements                              |

| DLY_RST    | Input     | SLOWCLK            | (Optional) This signal is available when you set <b>Delay Mode</b> to <b>dpa</b> or <b>dynamic</b> . Reset the delay counter or the DPA circuit, depending on the LVDS RX delay settings.                       |

| DBG[5:0]   | Output    | SLOWCLK            | DPA debug pin. Outputs the final delay chain settings when DPA achieved lock.                                                                                                                                   |

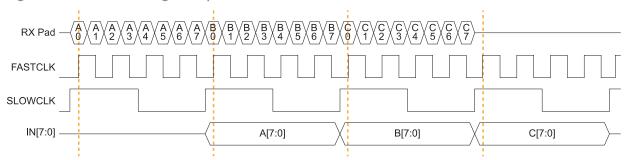

The following waveform shows the relationship between the fast clock, slow clock, RX data coming in from the pad, and byte-aligned data to the core.

Figure 28: LVDS RX Timing Example Serialization Width of 8 (Half Rate)

IN is byte-aligned data passed to the core on the rising edge of SLOWCLK.

**Note:** For LVDS RX interfaces with multiple LVDS RX lanes and an LVDS RX clock input, use the LVDS RX blocks from the same side of the FPGA to minimize skew between data lanes and RX clock input.

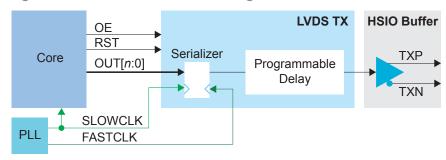

#### LVDS TX

You can configure an HSIO block as one LVDS TX signal. LVDS TX can be used in the serial data output mode or reference clock output mode.

Figure 29: LVDS TX Interface Block Diagram

Table 16: LVDS TX Signals (Interface to FPGA Fabric)

| Signal   | Direction | Clock<br>Domain | Description                                                                               |

|----------|-----------|-----------------|-------------------------------------------------------------------------------------------|

| OUT[9:0] | Input     | SLOWCLK         | Parallel output data from the core. The width is programmable.                            |

| SLOWCLK  | Input     | -               | Parallel (slow) clock.                                                                    |

| FASTCLK  | Input     | -               | Serial (fast) clock.                                                                      |

| RST      | Input     | SLOWCLK         | (Optional) This signal is available when serialization is enabled. Resets the serializer. |

| OE       | Input     | -               | (Optional) Output enable signal.                                                          |

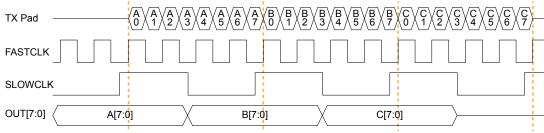

The following waveform shows the relationship between the fast clock, slow clock, TX data going to the pad, and byte-aligned data from the core.

Figure 30: LVDS Timing Example Serialization Width of 8 (Half Rate)

OUT is byte-aligned data passed from the core on the rising edge of SLOWCLK.

**Note:** For LVDS TX interfaces with multiple LVDS TX lanes and an LVDS TX reference clock output, use the LVDS TX blocks from the same side of the FPGA to minimize skew between data lanes and TX reference clock output.

#### LVDS Bidirectional

You can configure an HSIO block as one LVDS bidirectional signal. You must use the same serialization for the RX and TX.

Figure 31: LVDS Bidirectional Interface Block Diagram

Table 17: LVDS Bidirectional Signals (Interface to FPGA Fabric)

| Signal     | Direction | Clock<br>Domain    | Description                                                                                                                                                                                          |

|------------|-----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN[9:0]    | Output    | SLOWCLK            | Parallel input data to the core. The width is programmable.                                                                                                                                          |

| INSLOWCLK  | Input     | -                  | Parallel (slow) clock for RX.                                                                                                                                                                        |

| INFASTCLK  | Input     | -                  | Serial (fast) clock for RX.                                                                                                                                                                          |

| FIFO_EMPTY | Output    | FIFOCLK            | This signal is required when you turn on the <b>Enable Clock Crossing FIFO</b> option Indicates that the FIFO is empty.                                                                              |

| FIFOCLK    | Input     | -                  | This signal is required when you turn on the <b>Enable Clock Crossing FIFO</b> option. Core clock to read from the FIFO.                                                                             |

| FIFO_RD    | Input     | FIFOCLK            | This signal is required when you turn on the <b>Enable Clock Crossing FIFO</b> option. Enables FIFO to read.                                                                                         |

| INRST      | Input     | FIFOCLK<br>SLOWCLK | This signal is available when deserialization is enabled. Asynchronous. Resets the FIFO and RX deserializer. If the FIFO is enabled, it is relative to FIFOCLK; otherwise it is relative to SLOWCLK. |

| ENA        | Input     | -                  | Dynamically enable or disable the LVDS input buffer. Can save power when disabled.  1: Enabled 0: Disabled                                                                                           |

| TERM       | Input     | -                  | The signal is available when dynamic termination is enabled. Enables or disables termination in dynamic termination mode.  1: Enabled 0: Disabled                                                    |

| Signal     | Direction | Clock<br>Domain | Description                                                                                                                                                                                          |

|------------|-----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOCK       | Output    |                 | (Optional) This signal is available when you set <b>Delay Mode</b> to <b>dpa</b> . Indicates that the DPA has achieved training lock and data can be passed.                                         |

| DLY_ENA    | Input     | SLOWCLK         | This signal is required when you set <b>Delay Mode</b> to <b>dynamic</b> or <b>dpa</b> . Enable the dynamic delay control or the DPA circuit, depending on the bidirectional LVDS delay settings.    |

| DLY_INC    | Input     | SLOWCLK         | This signal is required when you set <b>Delay Mode</b> to <b>dynamic</b> . Dynamic delay control. Cannot be used with DPA enabled. When DLY_ENA is 1,                                                |

|            |           |                 | 1: Increments 0: Decrements                                                                                                                                                                          |

| DLY_RST    | Input     | SLOWCLK         | (Optional) This signal is available when you set <b>Delay Mode</b> to <b>dpa</b> or <b>dynamic</b> . Reset the delay counter or the DPA circuit, depending on the bidirectional LVDS delay settings. |

| DBG[5:0]   | Output    | SLOWCLK         | DPA debug pin. Outputs the final delay chain settings when DPA achieved lock.                                                                                                                        |

| OUT[9:0]   | Input     | SLOWCLK         | Parallel output data from the core. The width is programmable.                                                                                                                                       |

| OUTSLOWCLK | Input     | -               | Parallel (slow) clock for TX.                                                                                                                                                                        |

| OUTFASTCLK | Input     | -               | Serial (fast) clock for TX.                                                                                                                                                                          |

| OUTRST     | Input     | SLOWCLK         | This signal is available when serialization is enabled. Resets the TX serializer.                                                                                                                    |

| OE         | Input     | -               | Output enable signal.                                                                                                                                                                                |

#### LVDS Pads

Table 18: LVDS Pads

| Signal | Direction | Description         |

|--------|-----------|---------------------|

| Р      | Output    | Differential pad P. |

| N      | Output    | Differential pad N. |

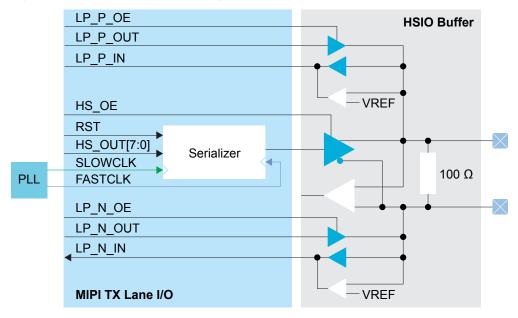

## **HSIO Configured as MIPI Lane**

You can configure the HSIO block as a MIPI RX or TX lane. The block supports bidirectional data lane, unidirectional data lane, and unidirectional clock lane which can run at speeds up to 1.5 Gbps. The MIPI lane operates in high-speed (HS) and low-power (LP) modes. In HS mode, the HSIO block transmits or receives data with x8 serializer/deserializer. In LP mode, it transmits or receives data without deserializer/serializer.

The MIPI lane block does not include the MIPI D-PHY core logic. A full MIPI D-PHY solution requires:

- Multiple MIPI RX or TX lanes (at least a clock lane and a data lane)

- Soft MIPI D-PHY IP core programmed into the FPGA fabric

The MIPI D-PHY standard is a point-to-point protocol with one endpoint (TX) responsible for initiating and controlling communication. Often, the standard is unidirectional, but when implementing the MIPI DSI protocol, you can use one TX data lane for LP bidirectional communication.

The protocol is source synchronous with one clock lane and 1, 2, 4, or 8 data lanes. The number of lanes available depends on which package you are using. A dedicated HSIO block is assigned on the RX interface as a clock lane while the clock lane for TX interface can use any of the HSIO block in the group.

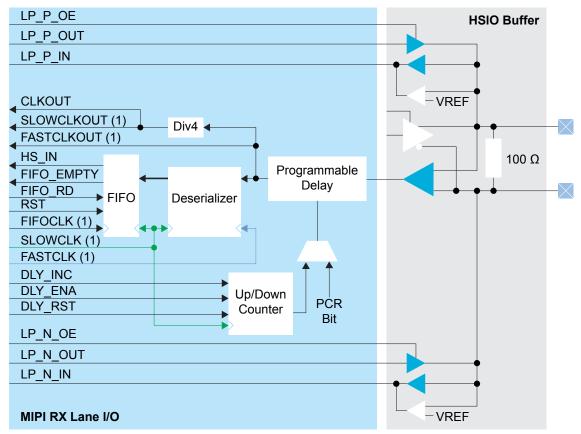

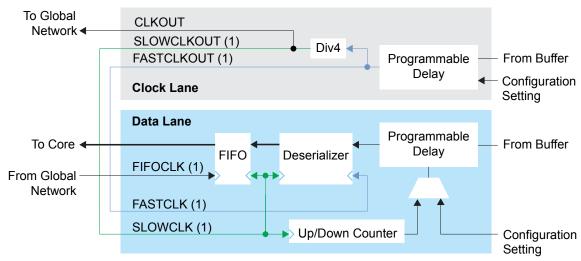

#### MIPI RX Lane

In RX mode, the HS (fast) clock comes in on the MIPI clock lane and is divided down to generate the slow clock. The fast and slow clocks are then passed to neighboring HSIO blocks to be used for the MIPI data lanes.

The data lane fast and slow clocks must be driven by a clock lane in the same MIPI group (dedicated buses drive from the clock lane to the neighboring data lanes).

The MIPI RX function is defined as:

**Table 19: MIPI RX Function**

| MIPI RX Function | Description                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------------------------|

| RX_DATA_xy_zz    | MIPI RX Data Lane. You can use any data lanes within the same group to form multiple lanes of MIPI RX channel. |

|                  | x = P  or  N                                                                                                   |

|                  | y = 0 to 7 data lanes (Up to 8 data lanes per channel)                                                         |

|                  | zz = 10 to 117 MIPI RX channel (Up to 18 MIPI RX channels)                                                     |

| RX_CLK_x_zz      | MIPI RX Clock Lane. One clock lane is required for each MIPI RX channel.                                       |

|                  | x = P  or  N                                                                                                   |

|                  | zz = 10 to 117 MIPI RX channel (Up to 18 MIPI RX channels)                                                     |

Figure 32: MIPI RX Lane Block Diagram

1. These signals are in the primitive, but the software automatically connects them for you.

Table 20: MIPI RX Lane Signals

Interface to MIPI soft CSI/DSI controller with D-PHY in FPGA Fabric

| Signal                    | Direction | Clock Domain       | Description                                                                                                                                                                                                             |

|---------------------------|-----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LP_P_OE                   | Input     | -                  | (Optional) LP output enable signal for P pad.                                                                                                                                                                           |

| LP_P_OUT                  | Input     | -                  | (Optional) LP output data from the core for the P pad.<br>Used if the data lane is reversible.                                                                                                                          |

| LP_P_IN                   | Output    | -                  | LP input data from the P pad.                                                                                                                                                                                           |

| CLKOUT                    | Output    | -                  | Divided down parallel (slow) clock from the pads that can drive the core clock tree. Used to drive the core logic implementing the rest of the D-PHY protocol. It should also connect to the FIFOCLK of the data lanes. |

| SLOWCLKOUT <sup>(5)</sup> | Output    | -                  | Divided down parallel (slow) clock from the pads. Can only drive RX DATA lanes.                                                                                                                                         |

| FASTCLKOUT <sup>(5)</sup> | Output    | -                  | Serial (fast) clock from the pads. Can only drive RX DATA lanes.                                                                                                                                                        |

| HS_IN[7:0]                | Output    | SLOWCLK            | High-speed parallel data input.                                                                                                                                                                                         |

| FIFO_EMPTY                | Output    | FIFOCLK            | (Optional) When the FIFO is enabled, this signal indicates that the FIFO is empty.                                                                                                                                      |

| FIFO_RD                   | Input     | FIFOCLK            | (Optional) Enables FIFO to read.                                                                                                                                                                                        |

| RST                       | Input     | FIFOCLK<br>SLOWCLK | (Optional) Asynchronous. Resets the FIFO and serializer. If the FIFO is enabled, it is relative to FIFOCLK; otherwise it is relative to SLOWCLK.                                                                        |

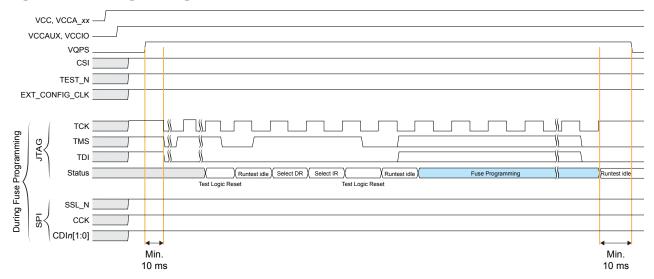

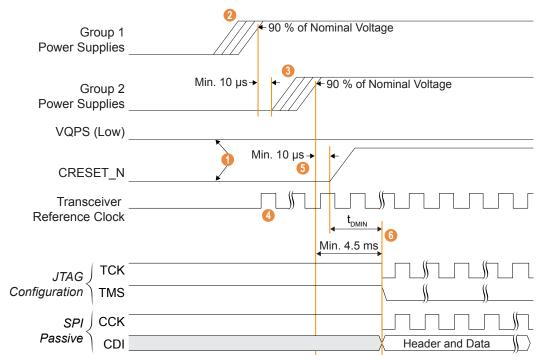

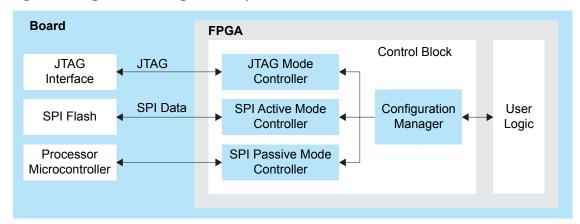

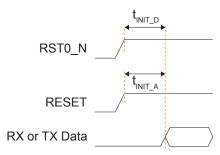

| FIFOCLK <sup>(5)</sup>    | Input     | -                  | (Optional) Core clock to read from the FIFO.                                                                                                                                                                            |