# **Efinity<sup>®</sup> Software User Guide**

UG-EFN-SOFTWARE-v15.0 November 2024 www.efinixinc.com

Copyright © 2024. All rights reserved. Efinix, the Efinix logo, the Titanium logo, the Topaz logo, Quantum, Trion, and Efinity are trademarks of Efinix, Inc. All other trademarks and service marks are the property of their respective owners. All specifications subject to change without notice.

# Contents

| Figures                                                                        | v   |

|--------------------------------------------------------------------------------|-----|

| Tables                                                                         | vii |

| Introduction                                                                   | iv  |

| New in v2024.2                                                                 |     |

| Using an Existing Project with a New Software Version                          |     |

| Where to Learn More                                                            |     |

| Hardware and Software Requirements                                             |     |

| Chapter 1: Setting Up                                                          |     |

| Efinity Quick Start                                                            |     |

| Setting General Tool Preferences                                               |     |

| Auto-Load Place-and-Route Data                                                 |     |

| Efinity Main Window                                                            |     |

| Chapter 2: Managing Projects                                                   |     |

| Project Editor                                                                 |     |

| Project Tab                                                                    |     |

| Referencing RTL Source Files                                                   |     |

| Using VHDL Libraries                                                           |     |

| Packaging Design Files<br>Migrating a Project to another FPGA                  |     |

|                                                                                |     |

| Chapter 3: Running the Tool Flow                                               |     |

| Run the Flow with the Dashboard Controls<br>Run the Flow from the Command Line |     |

| About Efinity <sup>®</sup> Synthesis                                           | 30  |

| Netlist Tab                                                                    |     |

| Netlist Viewer (Beta)                                                          |     |

| Opening the Netlist Viewer                                                     |     |

| Zooming                                                                        |     |

| Highlighting and Marking                                                       |     |

| Viewing the Netlist Hierarchy                                                  |     |

| Finding Elements                                                               |     |

| Viewing a User-Defined Element                                                 |     |

| Viewing an Element's Connectivity                                              |     |

| Viewing the Action History<br>Viewing Messages and Logs                        |     |

| Result Tab                                                                     |     |

| Viewing Place-and-Route Results                                                |     |

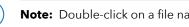

| Chapter 4: Using the IP Manager                                                | 40  |

| Supported IP Cores by Family                                                   |     |

| Using the IP Configuration Wizard                                              |     |

| Generated Files                                                                |     |

| Instantiating IP in Your Project                                               |     |

| Managing IP in Your Project                                                    |     |

| IP Settings File                                                               |     |

| Getting Updated IP                                                             |     |

| Chapter 5: Constraining Logic and Assigning Pins                               |     |

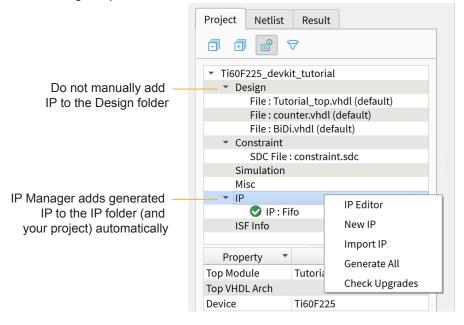

| About the Interface Designer                                                   |     |

| Get Oriented                                                                   |     |

| Using the Resource Assigner                                                    |     |

| Resource View                                                                  |     |

| Importing and Exporting Assignments<br>Interface Scripting File                |     |

|                                                                                |     |

| Contrations and Interafe as Destina                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 54 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Scripting an Interface Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

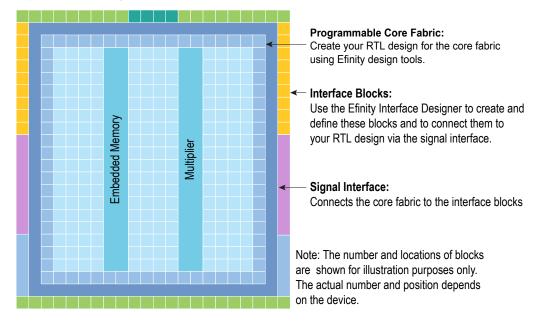

| Viewing the Package Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55 |

| Selecting a Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| Browsing for Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| Constraining Logic and Routing Manually (Beta)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| Tiles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| Working with Primitives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| Enabling Manual Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| Assignment Rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| Creating a Location Assignment File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| Constraining Routing Manually (Titanium Only, Beta)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| Chapter 6: Analyzing Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 68 |

| Chapter 7: Simulating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 69 |

| Simulation Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| Changing the Default Testbench Names                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| Simulate with the iVerilog Simulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| View Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| Simulate with the ModelSim Simulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| Simulate with the NCSim Simulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| Chapter 8: Debugging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 76 |

| Profile Editor Perspective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| Virtual I/O Debug Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| Logic Analyzer Debug Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| Debug Wizard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| Debug Perspective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| Logic Analyzer Perspective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| Virtual I/O Perspective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| Debugger Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| Concurrent Debugging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| Resource Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| Disable the Debug Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| Disable the Debug Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| Disable the Debug Core<br>Chapter 9: Debugging Transceivers (Beta)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| C C C C C C C C C C C C C C C C C C C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>About the Programmer GUI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>About the Programmer GUI<br>Edit the SPI Active Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>About the Programmer GUI<br>Edit the SPI Active Clock<br>Generate a Bitstream (Programming) File                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>About the Programmer GUI<br>Edit the SPI Active Clock<br>Generate a Bitstream (Programming) File<br>About the BRAM Initial Content Updater                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>About the Programmer GUI<br>Edit the SPI Active Clock<br>Generate a Bitstream (Programming) File<br>About the BRAM Initial Content Updater<br>Updating the BRAM Initial Content                                                                                                                                                                                                                                                                                                                                                                     |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>About the Programmer GUI<br>Edit the SPI Active Clock<br>Generate a Bitstream (Programming) File<br>About the BRAM Initial Content Updater<br>Updating the BRAM Initial Content<br>Using the Example Files                                                                                                                                                                                                                                                                                                                                          |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>About the Programmer GUI<br>Edit the SPI Active Clock<br>Generate a Bitstream (Programming) File<br>About the BRAM Initial Content Updater<br>Updating the BRAM Initial Content<br>Using the Example Files<br>Command-Line Interface                                                                                                                                                                                                                                                                                                                |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>About the Programmer GUI<br>Edit the SPI Active Clock<br>Generate a Bitstream (Programming) File<br>About the BRAM Initial Content Updater<br>Updating the BRAM Initial Content<br>Using the Example Files<br>Command-Line Interface<br>Working with Bitstreams                                                                                                                                                                                                                                                                                     |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>About the Programmer GUI<br>Edit the SPI Active Clock<br>Generate a Bitstream (Programming) File<br>About the BRAM Initial Content Updater<br>Updating the BRAM Initial Content<br>Using the Example Files<br>Command-Line Interface<br>Working with Bitstreams<br>Edit the Bitstream Header                                                                                                                                                                                                                                                        |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>About the Programmer GUI<br>Edit the SPI Active Clock<br>Generate a Bitstream (Programming) File<br>About the BRAM Initial Content Updater<br>Updating the BRAM Initial Content<br>Using the Example Files<br>Command-Line Interface<br>Working with Bitstreams<br>Edit the Bitstream Header<br>Bitstream Compression                                                                                                                                                                                                                               |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>About the Programmer GUI<br>Edit the SPI Active Clock<br>Generate a Bitstream (Programming) File<br>About the BRAM Initial Content Updater<br>Updating the BRAM Initial Content<br>Using the Example Files<br>Command-Line Interface<br>Working with Bitstreams<br>Edit the Bitstream Header<br>Bitstream Compression<br>Export to Raw Binary Format                                                                                                                                                                                                |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>About the Programmer GUI<br>Edit the SPI Active Clock<br>Generate a Bitstream (Programming) File<br>About the BRAM Initial Content Updater<br>Updating the BRAM Initial Content<br>Using the Example Files<br>Command-Line Interface<br>Working with Bitstreams<br>Edit the Bitstream Header<br>Bitstream Compression<br>Export to Raw Binary Format<br>Export to Raw Binary Format<br>Export to .svf Format                                                                                                                                        |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>About the Programmer GUI<br>Edit the SPI Active Clock<br>Generate a Bitstream (Programming) File<br>About the BRAM Initial Content Updater<br>Updating the BRAM Initial Content.<br>Using the Example Files<br>Command-Line Interface<br>Working with Bitstreams<br>Edit the Bitstream Header<br>Bitstream Compression<br>Export to Raw Binary Format<br>Export to .svf Format<br>Convert to Intel Hex Format at the Command Line                                                                                                                   |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>About the Programmer GUI<br>Edit the SPI Active Clock<br>Generate a Bitstream (Programming) File<br>About the BRAM Initial Content Updater<br>Updating the BRAM Initial Content<br>Using the Example Files<br>Command-Line Interface<br>Working with Bitstreams<br>Edit the Bitstream Header<br>Bitstream Compression<br>Export to Raw Binary Format<br>Export to .svf Format<br>Convert to Intel Hex Format at the Command Line<br>Combine Bitstreams and Other Files                                                                                                      |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>Flash Programmer GUI<br>Edit the SPI Active Clock.<br>Generate a Bitstream (Programming) File<br>About the BRAM Initial Content Updater<br>Updating the BRAM Initial Content<br>Using the Example Files<br>Command-Line Interface.<br>Working with Bitstreams<br>Edit the Bitstream Header<br>Bitstream Compression<br>Export to Raw Binary Format<br>Export to .svf Format<br>Convert to Intel Hex Format at the Command Line<br>Combine Bitstreams and Other Files<br>SPI Programming                                                             |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>About the Programmer GUI<br>Edit the SPI Active Clock<br>Generate a Bitstream (Programming) File<br>About the BRAM Initial Content Updater<br>Updating the BRAM Initial Content<br>Using the Example Files<br>Command-Line Interface<br>Working with Bitstreams<br>Edit the Bitstream Header<br>Bitstream Compression<br>Export to Raw Binary Format<br>Export to .svf Format<br>Convert to Intel Hex Format at the Command Line<br>Combine Bitstreams and Other Files<br>SPI Programming<br>Program a Single Image                                 |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>Flash Programmer GUI<br>Edit the SPI Active Clock<br>Generate a Bitstream (Programming) File<br>About the BRAM Initial Content Updater<br>Updating the BRAM Initial Content.<br>Using the Example Files<br>Command-Line Interface.<br>Working with Bitstreams<br>Edit the Bitstream Header<br>Bitstream Compression<br>Export to Raw Binary Format<br>Export to Asv Format<br>Convert to Intel Hex Format at the Command Line<br>Combine Bitstreams and Other Files<br>SPI Programming<br>Program A Single Image<br>Program Multiple Images (CBSEL) |    |

| Chapter 9: Debugging Transceivers (Beta)<br>Launching the Transceiver Debugger<br>Using the Transceiver Debugger<br>Transceiver Debugger Commands<br>Interpreting the Results<br>Chapter 10: Configuring an FPGA<br>FPGA Configuration Modes<br>Flash Programming Modes<br>About the Programmer GUI<br>Edit the SPI Active Clock<br>Generate a Bitstream (Programming) File<br>About the BRAM Initial Content Updater<br>Updating the BRAM Initial Content<br>Using the Example Files<br>Command-Line Interface<br>Working with Bitstreams<br>Edit the Bitstream Header<br>Bitstream Compression<br>Export to Raw Binary Format<br>Export to .svf Format<br>Convert to Intel Hex Format at the Command Line<br>Combine Bitstreams and Other Files<br>SPI Programming<br>Program a Single Image                                 |    |

| Program a Daisy Chain                               |                                        |

|-----------------------------------------------------|----------------------------------------|

| JTAG Programming                                    |                                        |

| JTAG Device IDs                                     |                                        |

| Program a Single Image                              |                                        |

| Program Using a JTAG Chain                          |                                        |

| Program using a JTAG Bridge (New)                   |                                        |

| Program using a JTAG Bridge (Legacy)                |                                        |

| JTAG Programming with FTDI Chip Hardware            |                                        |

| FDTI Programming at the Command Line                |                                        |

| Using the Command-Line Programmer                   |                                        |

| Project-Based Programming Options                   |                                        |

| Configuration Status Register                       |                                        |

| Verifying Configuration with the Programmer         |                                        |

| Securing Titanium Bitstreams                        |                                        |

| Using the Efinity Bitstream Security Key Generator  |                                        |

| Blowing Fuses with the SVF Player                   |                                        |

| Enabling Security for Your Project                  |                                        |

| Encrypt or Sign Bitstreams from the Command Line    |                                        |

| Workflow for Using Security Features                |                                        |

| Verifying Security Settings                         |                                        |

| Chapter 11: Working with JTAG .svf Files            |                                        |

| Using the Efinity SVF Player                        |                                        |

|                                                     |                                        |

| Chapter 12: Working with Remote Hardware            |                                        |

| Appendix: Installing USB Drivers                    |                                        |

| Installing the Linux USB Driver                     |                                        |

| Installing the Windows USB Driver                   |                                        |

| Appendix: Connecting Programming Hardware           |                                        |

| SPI Programming Connections                         |                                        |

| JTAG Programming Connections (Trion FPGAs)          |                                        |

| JTAG Programming Connections (Titanium Topaz FPGAs) |                                        |

| Appendix: Efinity Tools                             |                                        |

| Appendix: Efinity Project Files                     | 143                                    |

| Efinity Source Files for Version Control            |                                        |

| Bitstream Generation                                |                                        |

| Debugger                                            |                                        |

| Interface Designer                                  |                                        |

| Unified Design Flow                                 |                                        |

| IP                                                  |                                        |

| Placement                                           |                                        |

| Project                                             |                                        |

| Routing                                             |                                        |

| Synthesis                                           |                                        |

| Appendix: Shortcuts                                 |                                        |

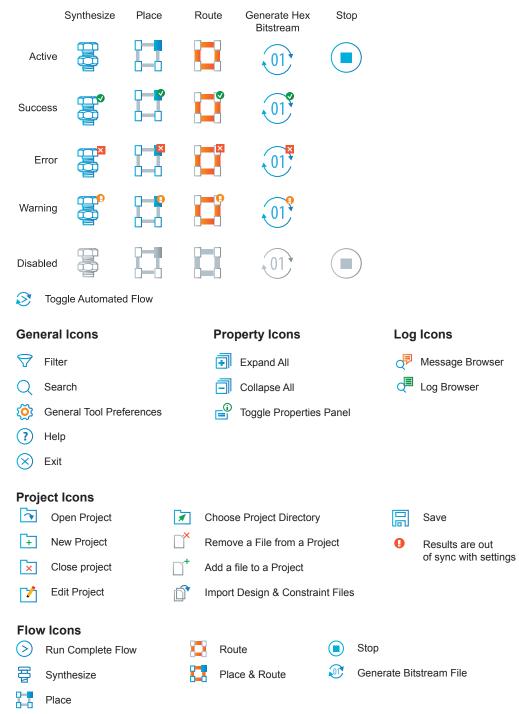

| Appendix: Icon List                                 |                                        |

| Revision History                                    | 150                                    |

|                                                     | ······································ |

# **Figures**

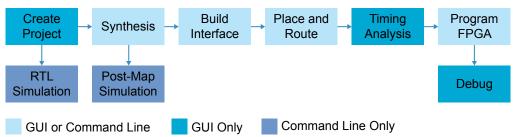

| Figure 1: Design Flow Overview                            | ix |

|-----------------------------------------------------------|----|

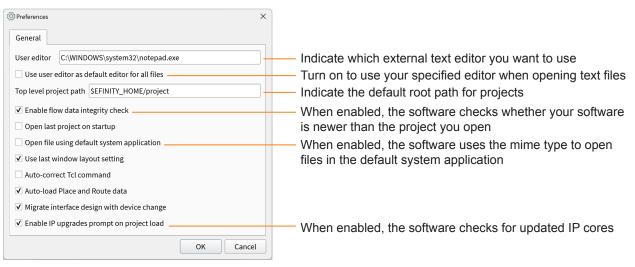

| Figure 2: General Tool Preferences                        |    |

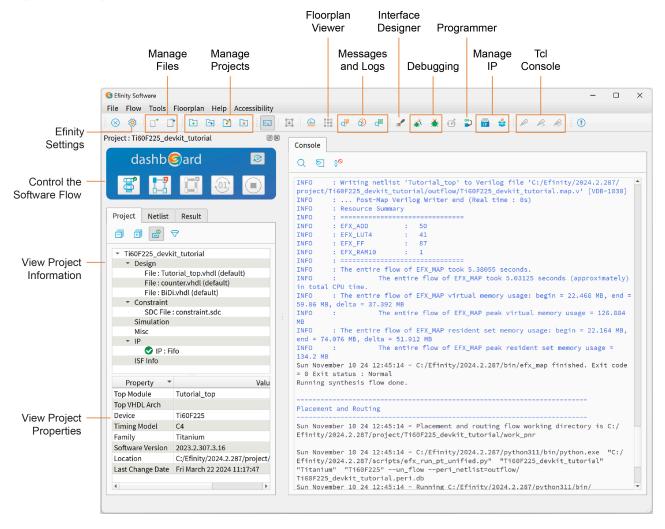

| Figure 3: Efinity Main Window                             | 17 |

| Figure 4: Project Editor - Project Tab                    | 18 |

| Figure 5: Project Editor - Design Tab                     |    |

| Figure 6: Project Editor - Synthesis Tab                  |    |

| Figure 7: Project Editor - Place and Route Tab            | 22 |

| Figure 8: Project Editor - Bitstream Generation Tab       | 22 |

| Figure 9: Project Editor - Debugger Tab                   |    |

| Figure 10: Project Tab                                    | 23 |

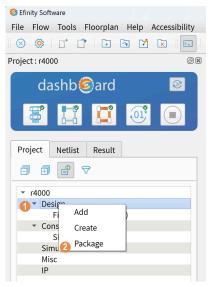

| Figure 11: Opening IP Packager                            | 26 |

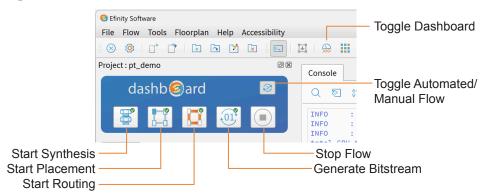

| Figure 12: Dashboard Controls                             | 29 |

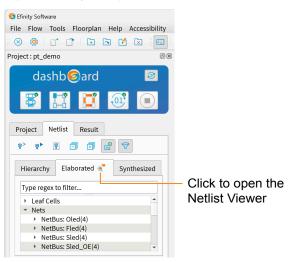

| Figure 13: Using the Netlist Tab                          |    |

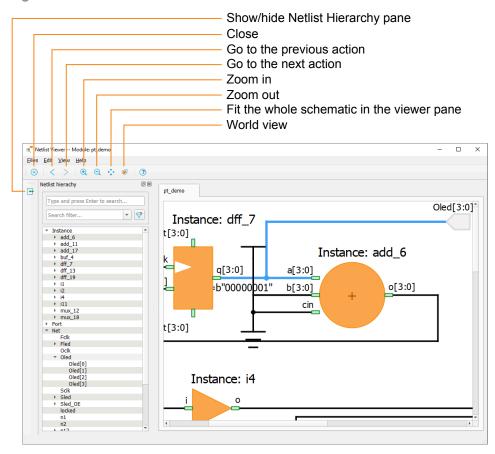

| Figure 14: Netlist Viewer                                 |    |

| Figure 15: Opening the Netlist Viewer                     |    |

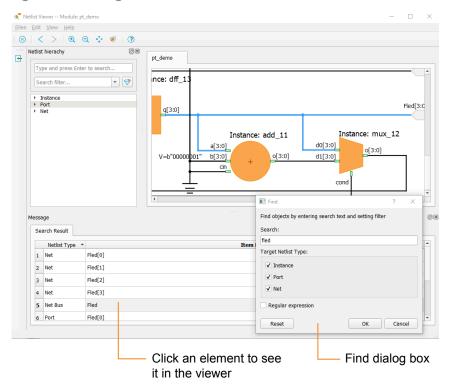

| Figure 16: Finding Elements                               | 34 |

| Figure 17: Using the Result Tab                           |    |

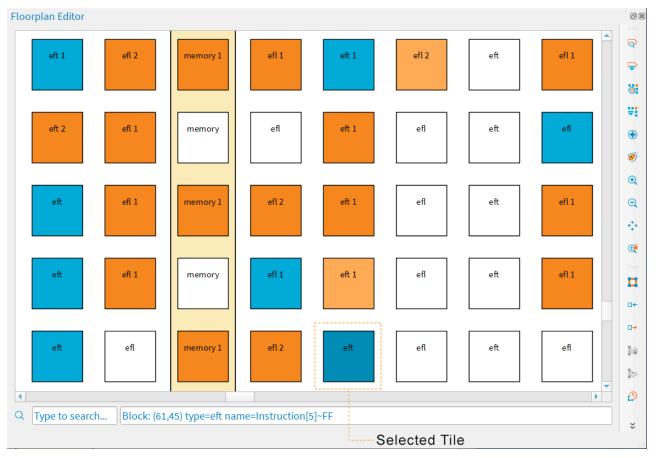

| Figure 18: Floorplan Editor                               | 39 |

| Figure 19: Project Tab > IP Folder Context-Sensitive Menu | 45 |

| Figure 20: Conceptual View of Interface Blocks            |    |

| Figure 21: Interface Designer                             | 49 |

| Figure 22: Resource Assigner                              | 50 |

| Figure 23: Resource View                                  | 52 |

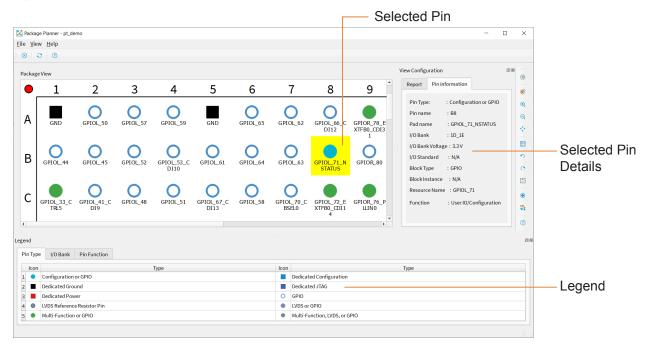

| Figure 24: Package Planner                                | 55 |

| Figure 25: Selected Pin                                   | 56 |

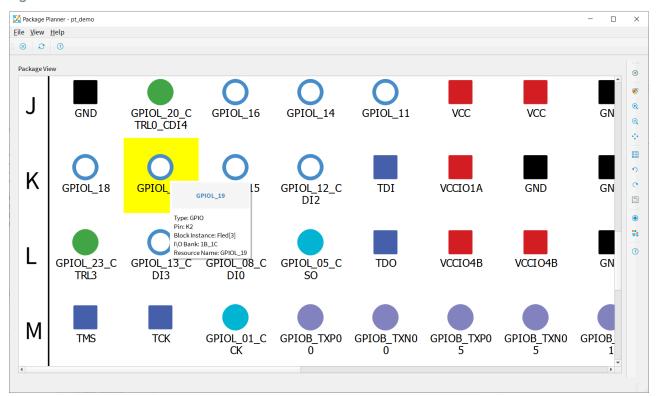

| Figure 26: Pin Quick View                                 | 56 |

| Figure 27: Browsing for Pins                              | 57 |

| Figure 28: Tiles in the Floorplan Editor                  |    |

| Figure 29: Bevhavioral Simulation Example .do Macro       | 74 |

| Figure 30: Post-Synthesis Simulation Example .do Macro    | 74 |

| Figure 31: Debugger Profile Editor Perspective            | 77 |

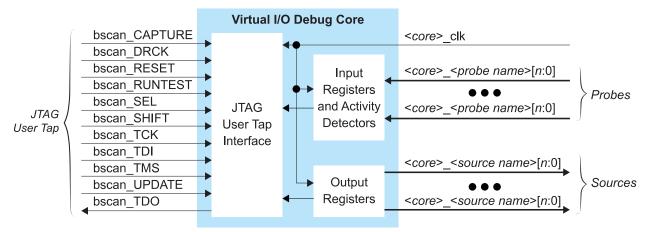

| Figure 32: Virtual I/O Core Block Diagram                                                                        | 78  |

|------------------------------------------------------------------------------------------------------------------|-----|

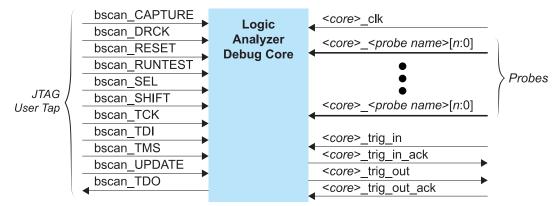

| Figure 33: Logic Analyzer Core Block Diagram                                                                     | 80  |

| Figure 34: Debug Perspective GUI - Logic Analyzer                                                                | 84  |

| Figure 35: Virtual I/O Debugger                                                                                  | 85  |

| Figure 36: Efinity Transceiver Debugger                                                                          | 88  |

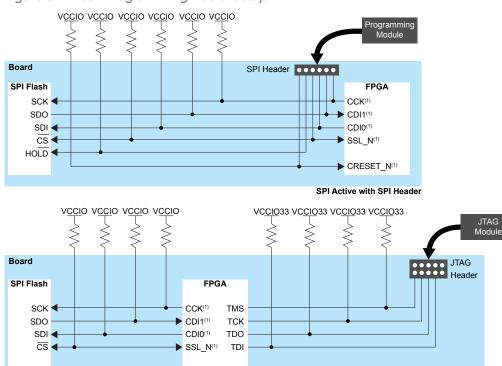

| Figure 37: Flash Programming Board Setup                                                                         | 92  |

| Figure 38: Programmer                                                                                            | 93  |

| Figure 39: Using the Netlist Pane                                                                                | 97  |

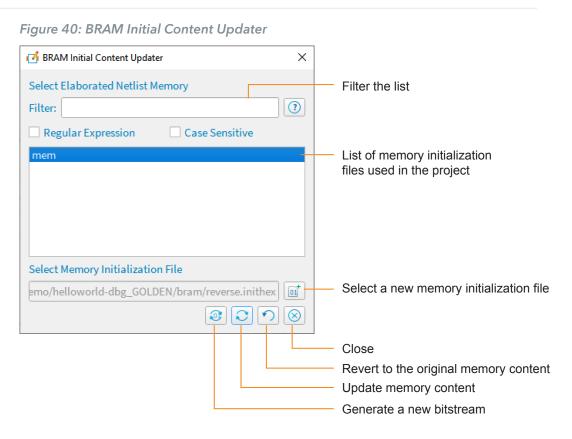

| Figure 40: BRAM Initial Content Updater                                                                          | 98  |

| Figure 41: Setting Programming Options (Trion)                                                                   | 117 |

| Figure 42: Setting Programming Options (Titanium Topaz)                                                          | 118 |

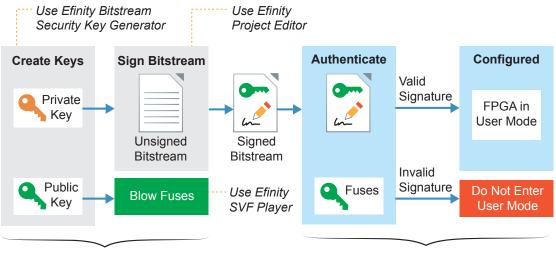

| Figure 43: Bitstream Authentication                                                                              | 121 |

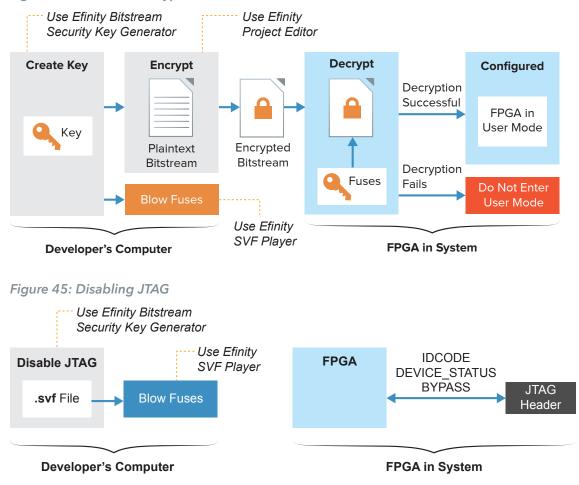

| Figure 44: Bitstream Encryption                                                                                  | 122 |

| Figure 45: Disabling JTAG                                                                                        | 122 |

| Figure 46: Efinity Bitstream Security Key Generator                                                              | 123 |

| Figure 47: SVF Player                                                                                            | 125 |

| Figure 48: Advanced Device Configuration Status Security Signals                                                 | 130 |

| Figure 49: SVF Player                                                                                            | 132 |

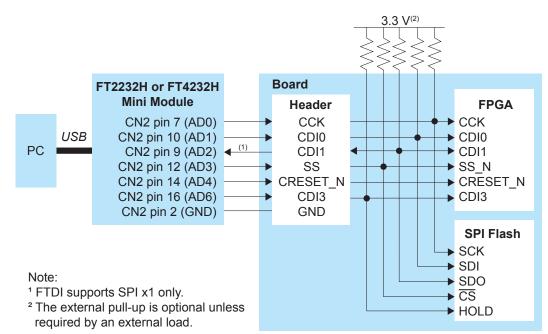

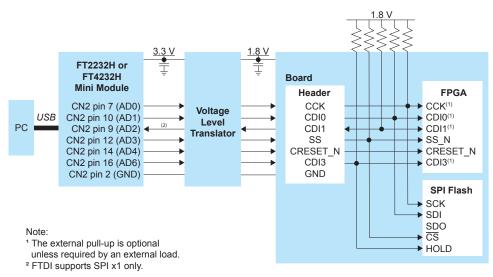

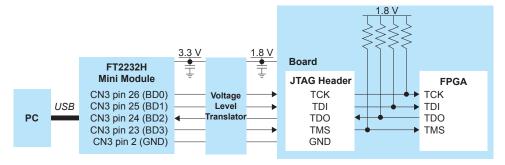

| Figure 50: SPI Flash Programming with FTDI FT2232H and FT4232H Mini Module Connections<br>(Trion FPGAs)          | 137 |

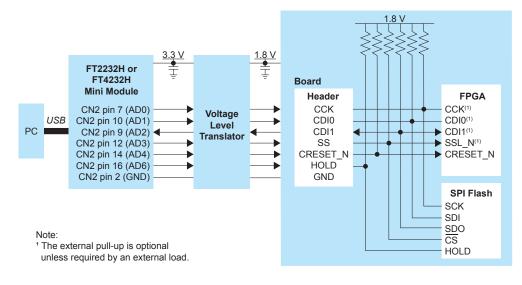

| Figure 51: SPI Flash 1.8V Programming with FTDI FT2232H and FT4232H Mini-Module<br>Connections                   | 137 |

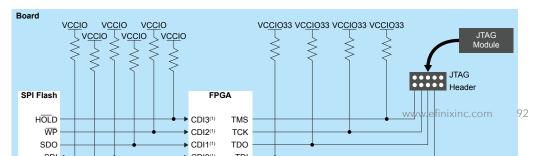

| Figure 52: SPI Flash Programming with FTDI FT2232H and FT4232H Mini Module Connections<br>(Titanium Topaz FPGAs) | 138 |

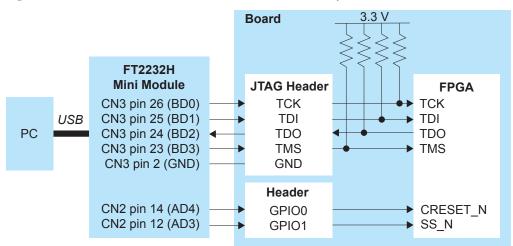

| Figure 53: Connect FT2232 Mini Module to JTAG Pins plus CRESET_N and SS_N                                        | 138 |

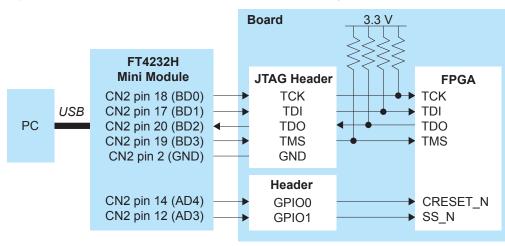

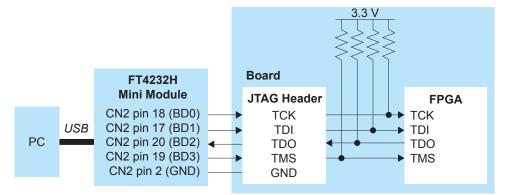

| Figure 54: Connect FT4232 Mini Module to JTAG Pins plus CRESET_N and SS_N                                        | 139 |

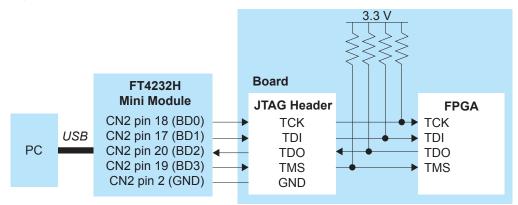

| Figure 55: Connect FT2232 Mini Module to JTAG Pins                                                               | 139 |

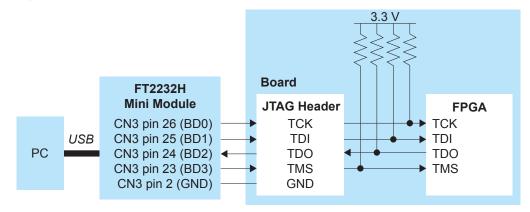

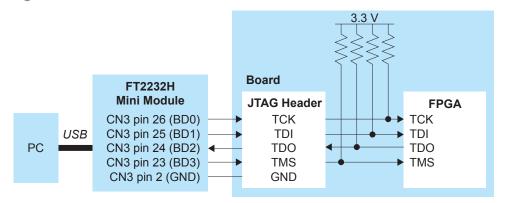

| Figure 56: Connect FT4232 Mini-Module to JTAG Pins                                                               | 139 |

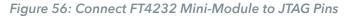

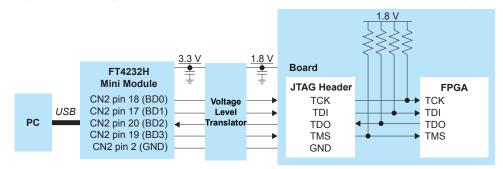

| Figure 57: Connect FT2232 Mini-Module to JTAG Pins                                                               | 140 |

| Figure 58: Example of FT2232 Mini-Module Connected to JTAG Pins Using 1.8V                                       | 140 |

| Figure 59: Connect FT4232 Mini-Module to JTAG Pins                                                               | 140 |

| Figure 60: Example of FT4232 Mini-Module Connected to JTAG Pins Using 1.8V                                       | 141 |

# **Tables**

| Table 1: Titanium FPGAs Supported in Efinity Software v2024.2 | ix   |

|---------------------------------------------------------------|------|

| Table 2: Topaz FPGAs Supported in Efinity Software v2024.2    | x    |

| Table 3: Trion FPGAs Supported in Efinity Software v2024.2    | x    |

| Table 4: Machine Memory Requirements                          | xii  |

| Table 5: Linux Operating System                               | xiii |

| Table 6: Synthesis Project Settings                           | 20   |

| Table 7: Compilation Files and Reports                        |      |

| Table 8: Interface Designer Files                             |      |

| Table 9: IP Cores Supported by Family                         | 41   |

| Table 10: End of Life IP Cores by Family                      |      |

| Table 11: Example GPIO .csv File                              |      |

| Table 12: FPGA Tile Types                                     |      |

| Table 13: Mapping Trion Primitives to Tiles and Sub-Blocks    |      |

| Table 14: Mapping Titanium Primitives to Tiles and Sub-Blocks |      |

| Table 15: Mapping Primitives to Tiles                         | 61   |

| Table 16: Core Primitive Simulation Models                    |      |

| Table 17: Interface Primitive Simulation Models               | 70   |

| Table 18: Virtual I/O Core Ports                              |      |

| Table 19: Logic Analyzer Core Ports                           | 80   |

| Table 20: Debugger Options                                    |      |

| Table 21: Transceiver Debugger Commands                       | 90   |

| Table 22: FPGA Configuration Modes                            |      |

| Table 23: Flash Programming Modes                             |      |

| Table 24: Internal Oscillator Clock Settings                  |      |

| Table 25: BRAM Initial Content Updater CLI Options            | 100  |

| Table 26: Modes when Combining Images                         |      |

| Table 27: Topaz JTAG Device IDs                               |      |

| Table 28: Titanium JTAG Device IDs                            |      |

| Table 29: Trion JTAG Device IDs                               |      |

| Table 30: Project-Specific Programming Options                | 115  |

| Table 31: Configuration Status Register                       | 119  |

| Table 32: Efinity Tools Used for Securing Bitstreams | 121 |

|------------------------------------------------------|-----|

| Table 33: Project Options for Security               | 126 |

| Table 34: AddSecurityTitanium.py Options             | 127 |

| Table 35: USB Programming Connections                | 135 |

| Table 36: Efinity Tools                              | 142 |

| Table 37: Shortcuts                                  | 155 |

| Table 38: Document Revision History                  | 159 |

|                                                      |     |

# Introduction

The Efinity<sup>®</sup> software provides a complete tool flow for designing with Efinix<sup>®</sup> FPGAs and cores. The graphical user interface (GUI) provides a visual way for you to set up projects, run the software flow, view floorplan information, and build the interfaces that surround the logic portion of your design. You use the command-line to perform simulation and automate the flow using scripts.

### Figure 1: Design Flow Overview

|  | Table 1: Titanium | FPGAs Supported in | n Efinity® Software | v2024.2 <sup>(1)</sup> |

|--|-------------------|--------------------|---------------------|------------------------|

|--|-------------------|--------------------|---------------------|------------------------|

| FPGA  | Package                               | Bitstream    | Timing      | Pinout      |

|-------|---------------------------------------|--------------|-------------|-------------|

| Ti35  | F100S3F2, F225                        | $\checkmark$ | Final       | Final       |

|       | F100                                  | $\checkmark$ | Final       | Final       |

|       | F256                                  | $\checkmark$ | Final       | Final       |

| Ti60  | W64, F100S3F2                         | $\checkmark$ | Final       | Final       |

|       | F100                                  | $\checkmark$ | Final       | Final       |

|       | F225                                  | $\checkmark$ | Final       | Final       |

|       | F256                                  | $\checkmark$ | Final       | Final       |

| Ti85  | N676                                  | -            | Preliminary | Preliminary |

| Ti90  | J361, G400, J484, L484, G529          | $\checkmark$ | Final       | Final       |

| Ti120 | J361, G400, J484, L484, G529          | $\checkmark$ | Final       | Final       |

| Ti135 | N676                                  | -            | Preliminary | Preliminary |

| Ti165 | C529, N1156, N484                     | -            | Preliminary | Preliminary |

| Ti180 | J361, G400, J484,<br>L484, M484, G529 | ~            | Final       | Final       |

| Ti240 | C529, N1156, N484                     | -            | Preliminary | Preliminary |

| Ti375 | C529, N1156                           | $\checkmark$ | Preliminary | Final       |

|       | N484                                  | -            | Preliminary | Preliminary |

<sup>&</sup>lt;sup>(1)</sup> Refer to the release notes on the web site for the latest support. Software patches often enable new device support.

Table 2: Topaz FPGAs Supported in Efinity<sup>®</sup> Software v2024.2<sup>(2)</sup>

| FPGA         | Package          | Bitstream | Timing      | Pinout |

|--------------|------------------|-----------|-------------|--------|

| Tz50         | F100, F225, F256 | ~         | Preliminary | Final  |

| Tz110, Tz170 | J361             | -         | Preliminary | Final  |

|              | G400, J484       | _         | Preliminary | Final  |

| Table 3: Trion | FPGAs Supported | in Efinity <sup>®</sup> Software | v2024.2 |

|----------------|-----------------|----------------------------------|---------|

|----------------|-----------------|----------------------------------|---------|

| FPGA           | Package                                      | Bitstream | Timing | Pinout      |

|----------------|----------------------------------------------|-----------|--------|-------------|

| T4             | F49, F81                                     | ~         | Final  | Final       |

| Т8             | F49, F81, Q144                               | ~         | Final  | Final       |

| T13            | Q100F3, F169, F256                           | ~         | Final  | Final       |

| T20            | W80, Q100F3, F169,<br>Q144, F256, F324, F400 | ~         | Final  | Final       |

| Т35            | F324, F400                                   | ~         | Final  | Final       |

|                | F256                                         | -         | Final  | Preliminary |

| T55, T85, T120 | F324, F484, F576                             | ~         | Final  | Final       |

### New in v2024.2

The Efinity<sup>®</sup> software v2024.2 has the following new features and enhancements:

- Support for Topaz FPGAs

- Tz50 in F100, F225, and F256 packages

- Tz110 in J361, G400, and J484 packages

- Tz170 in J361, G400, and J484 packages

- Improvements to PMA Direct mode support

- 40% reduction in peak memory use for Titanium FPGAs

- Unified design feature

- Simulation support for basic interface blocks

- Synthesis inferencing and instantiation support for basic functions

- Integration with Efinity GUI

- Improved SDC support

- All functions support Tcl objects

- New commands check\_timing and report\_cdc to help users improve SDC quality

<sup>&</sup>lt;sup>(2)</sup> Refer to the release notes on the web site for the latest support. Software patches often enable new device support.

# Using an Existing Project with a New Software Version

If you are upgrading from an older Efinity version, previously generated compilation files (such as old synthesis and place and route output files) may not be compatible with the new version of Efinity software. If the old files are not compatible, the software will prompt you to re-compile.

**Important:** When you open an existing project in a newer software version the Efinity software updates the project files with version-specific modeling information; the project files are not backwards compatible. Therefore, Efinix recommends that you make a backup of your project if you may want to open it again in an previous software version.

### Where to Learn More

The Efinity<sup>®</sup> software includes documentation as PDF user guides and on-line HTML help. This documentation is provided with the software. You can also access the latest versions of PDF documentation in the Support Center:

- Efinity Software User Guide

- Efinity Synthesis User Guide

- Efinity Timing Closure User Guide

- Efinity Software Installation User Guide

- Efinity Trion Tutorial

- Efinity Debugger Tutorial

- Titanium Interfaces User Guide

- Trion Interfaces User Guide

- Efinity Interface Designer Python API

- Quantum<sup>®</sup> Trion Primitives User Guide

- Quantum<sup>®</sup> Titanium Primitives User Guide

- Quantum<sup>®</sup> Topaz Primitives User Guide

In addition to documentation, Efinix field application engineers have created a series of videos to help you learn about aspects of the software. You can view these videos in the Support Center.

# Hardware and Software Requirements

### **General Requirements**

- Efinity full release: 64-bit, x86 instruction set architecture

- Windows Standalone Programmer.

- Windows 10: 64-bit x86 instruction set architecture.

- Windows 11: 64-bit x86 instruction set architecture.

- Computer with a 64-bit operating system.

- A 64-bit Windows system is required for the Efinity standalone programmer.

- A 64-bit Windows system is required for using the security tools in the Efinity standalone programmer.

- Your preferred text editor such as Notepad, gVim, Visual Studio

- Machine memory requirements (when running Efinity design compilations):

#### Table 4: Machine Memory Requirements

| Product  | Model                                                | Memory |

|----------|------------------------------------------------------|--------|

| Trion    | T4, T8, T13, T20, T35                                | 8 GB   |

|          | T55, T85, T120                                       | 16 GB  |

| Titanium | Ti35, Ti60                                           | 8 GB   |

|          | Ti85, Ti90, Ti120, Ti135, Ti180, Ti165, Ti240, Ti375 | 16 GB  |

| Тораz    | Tz50                                                 | 8 GB   |

|          | Tz110, Tz170                                         | 16 GB  |

### Windows Requirements

- Windows 10 or later, 64 bit operating system

- Microsoft Visual C+ + 2019 x64 runtime library (or latest version) redistributable https://learn.microsoft.com/en-us/cpp/windows/latest-supported-vc-redist? view=msvc-170

i

**Note:** If you want to use the stand-alone Programmer, you also need to install the x86 and x64 libraries (for 64-bit systems).

- Zadig software to install USB drivers see Installing the Windows USB Driver on page 136

- Java 64-bit runtime environment; required for configuring the Sapphire RISC-V SoC and DMA Controller in the IP Manager; available from:

- https://www.java.com/en/download/manual.jsp (Java 8)

- https://developers.redhat.com/products/openjdk/download (OpenJDK 8 or 11)

- http://jdk.java.net/16/ (OpenJDK 16)

**Note:** You may also use other Java software platforms that are available in the market.

**Note:** The path <*drive*>:**\Windows\System32** must exist in %PATH% if you have a customized environment variable.

### Linux Requirements

### Table 5: Linux Operating System

| Operating System                    | Note                                                                                                                                                                                                                                                                   |  |  |  |  |  |