# Titanium Interfaces User Guide

UG-TiINTF-v5.6 January 2025 www.efinixinc.com

Copyright © 2025. All rights reserved. Efinix, the Efinix logo, the Titanium logo, the Topaz logo, Quantum, Trion, and Efinity are trademarks of Efinix, Inc. All other trademarks and service marks are the property of their respective owners. All specifications subject to change without notice.

# Contents

| About the Interface Designer                              | v  |

|-----------------------------------------------------------|----|

| Chapter 1: Get Oriented                                   | 6  |

| Interface Blocks                                          | 9  |

| Package/Interface Support Matrix                          |    |

| Interface Block Connectivity                              |    |

| Clocking Interface Blocks                                 |    |

| Designing an Interface                                    |    |

| Create or Delete a Block                                  |    |

| Using the Resource Assigner                               |    |

| Resource View                                             |    |

| Importing and Exporting Assignments                       |    |

| Viewing the Package Pinout                                |    |

| Selecting a Pin                                           |    |

| Browsing for Pins                                         |    |

| Interface Designer Output Files                           |    |

| Scripting an Interface Design                             |    |

| Chapter 2: Device Settings                                | 23 |

| Configuration Interface                                   |    |

| Enable Internal Reconfiguration                           |    |

| Enable User Status Pin                                    |    |

| Enable External Access to Flash                           |    |

| About SEU Detection                                       |    |

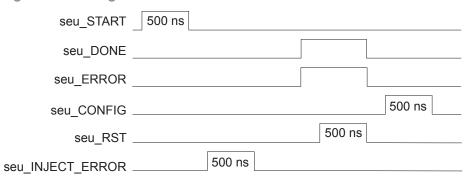

| Enable SEU Detection                                      |    |

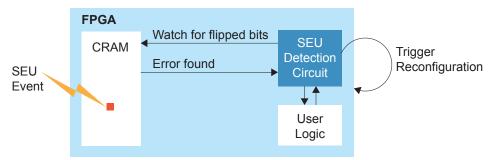

| SEU Detection Circuitry                                   |    |

| Design Check: SEU Messages                                |    |

| Design Check: Configuration Messages                      |    |

| I/O Banks Interface                                       |    |

| Titanium I/O Banks                                        |    |

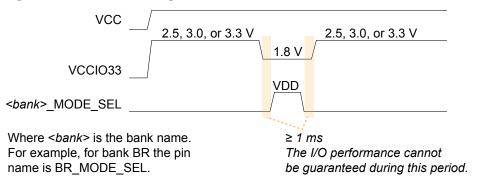

| Dynamic Voltage Support                                   |    |

| Design Check: I/O Bank Messages                           |    |

| Chapter 3: Clock and Control Networks                     |    |

| Clock Sources that Drive the Global and Regional Networks |    |

| Configuring the Dynamic Clock Multiplexers                |    |

| Driving both the Global and Regional Networks             |    |

| Design Check: Clock Control Messages                      |    |

| Chapter 4: DDR Interface                                  |    |

| About the DDR DRAM Interface                              |    |

|                                                           |    |

| Using the DDR Interface                                   |    |

| Design Check: DDR Messages                                |    |

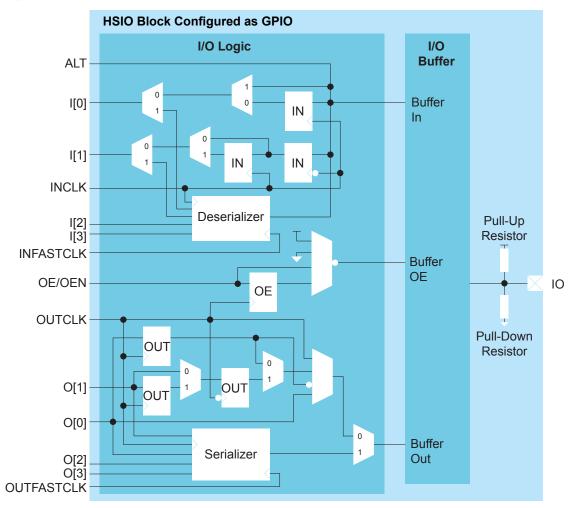

| Chapter 5: GPIO Interface                                 |    |

| Types of GPIO                                             |    |

| Features for HVIO and HSIO Configured as GPIO             |    |

| Double-Data I/O                                           |    |

| Programmable Delay Chains                                 |    |

| About the HVIO Interface                                  |    |

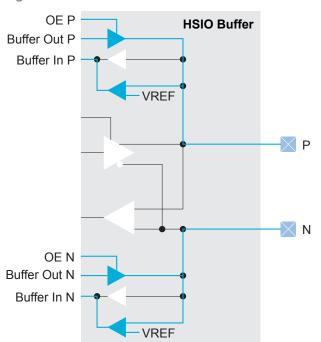

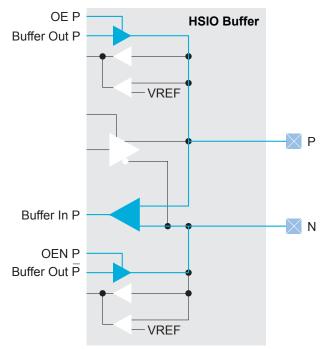

| About the HSIO Interface                                  |    |

| HSIO Configured as GPIO                                   |    |

| Using the GPIO Block                                      |    |

| Using the GPIO Bus Block                                  |    |

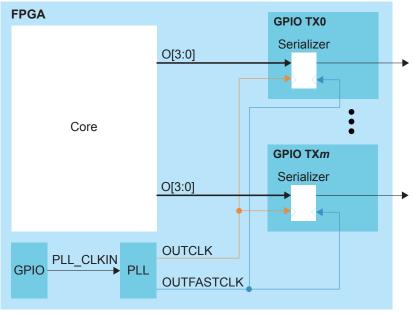

| Create a TX Serializer Interface                          |    |

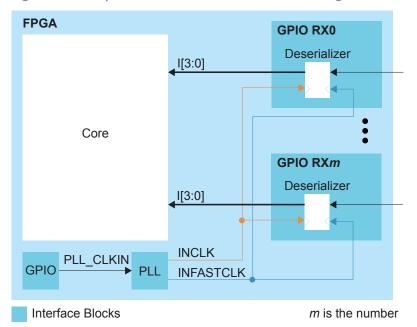

| Create a RX Deserializer Interface                        |    |

| Design Check: GPIO Messages                               | 77 |

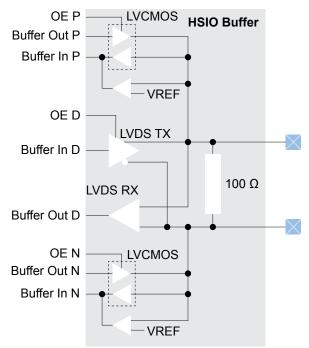

| Chapter 6: LVDS Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HSIO Configured as LVDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                       |

| Using the LVDS Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                       |

| Create an LVDS TX Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                       |

| Create an LVDS RX Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                       |

| Design Check: LVDS Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 102                                                                                                                                                                                                                   |

| Chamber 7: Thurse DAM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 440                                                                                                                                                                                                                   |

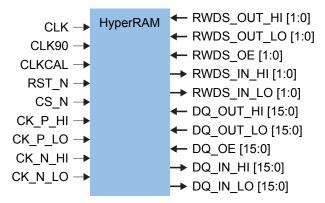

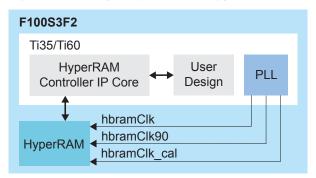

| Chapter 7: HyperRAM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                       |

| About the HyperRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       |

| Using the HyperRAM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                       |

| Design Check: HyperRAM Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Z                                                                                                                                                                                                                     |

| Chapter 8: JTAG User TAP Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 114                                                                                                                                                                                                                   |

| JTAG Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 114                                                                                                                                                                                                                   |

| Using the JTAG User TAP Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                       |

| Design Check: JTAG User Tap Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                       |

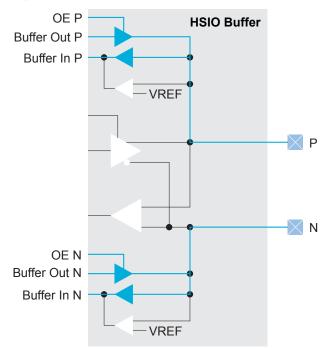

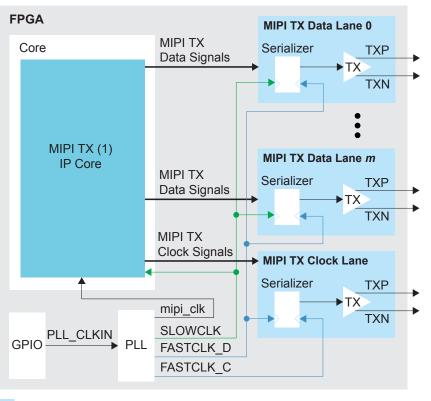

| Chapter 9: MIPI RX/TX Lane Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                       |

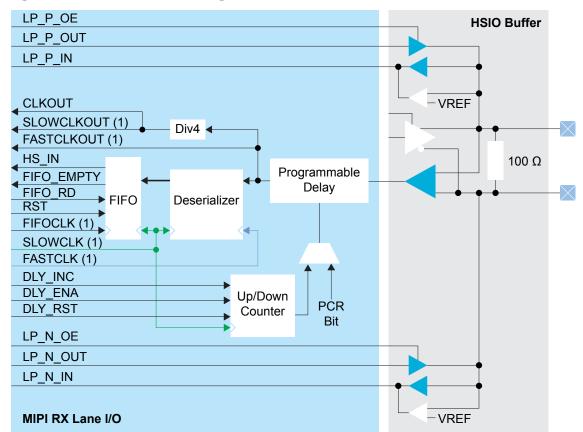

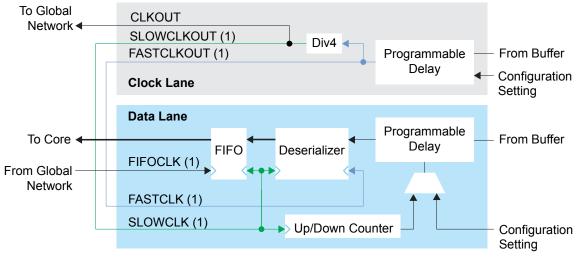

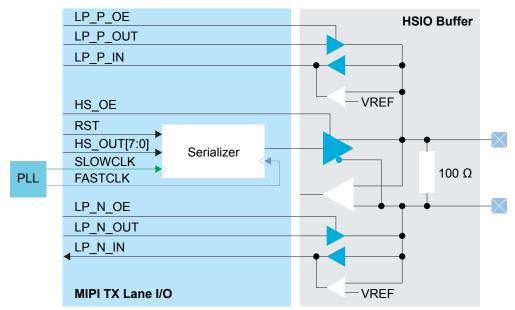

| HSIO Configured as MIPI Lane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                       |

| MIPI Groups by Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                       |

| Using the MIPI TX Lane or MIPI RX Lane Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                       |

| Create a MIPI TX Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                       |

| Create a MIPI RX Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                       |

| Design Check: MIPI Lane Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 126                                                                                                                                                                                                                   |

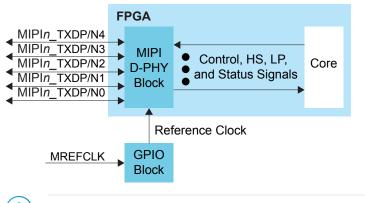

| Chapter 10: MIPI D-PHY Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 120                                                                                                                                                                                                                   |

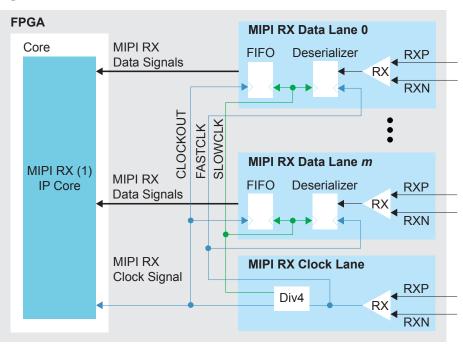

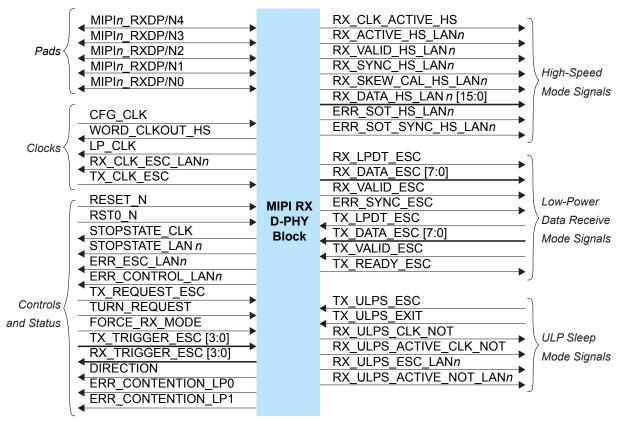

| MIPI RX D-PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                       |

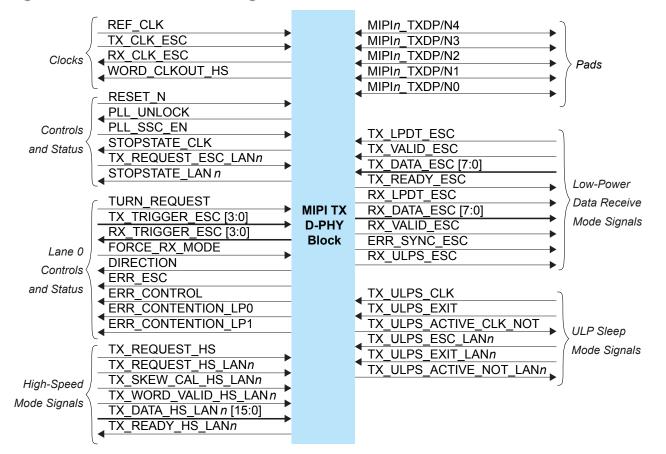

| MIPT NX D-1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                       |

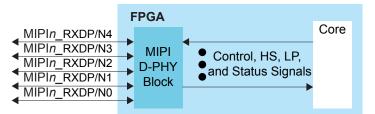

| Using the MIPI DPHY RX Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |

| Using the MIPI DPHY TX Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 141                                                                                                                                                                                                                   |

| Design Check: MIPI DPHY Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |

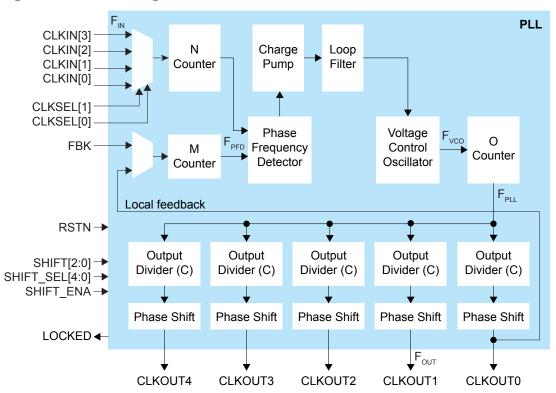

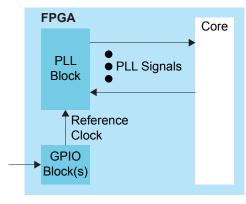

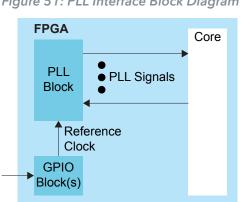

| Chapter 11: PLL Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 143                                                                                                                                                                                                                   |

| Chapter 11: PLL Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>143</b><br>143                                                                                                                                                                                                     |

| Chapter 11: PLL Interface<br>About the PLL Interface<br>Using the PLL Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>143</b><br>143<br>147                                                                                                                                                                                              |

| Chapter 11: PLL Interface<br>About the PLL Interface<br>Using the PLL Block<br>Using the PLL Clock Calculator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>143</b><br>143<br>147<br>147                                                                                                                                                                                       |

| Chapter 11: PLL Interface<br>About the PLL Interface<br>Using the PLL Block<br>Using the PLL Clock Calculator<br>Manually Configuring the PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b> 143</b><br>143<br>147<br>147<br>148                                                                                                                                                                               |

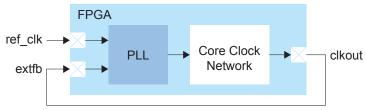

| Chapter 11: PLL Interface<br>About the PLL Interface<br>Using the PLL Block<br>Using the PLL Clock Calculator<br>Manually Configuring the PLL<br>Implementing a Zero-Delay Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>143</b><br>143<br>147<br>147<br>148<br>148                                                                                                                                                                         |

| Chapter 11: PLL Interface<br>About the PLL Interface<br>Using the PLL Block<br>Using the PLL Clock Calculator<br>Manually Configuring the PLL<br>Implementing a Zero-Delay Buffer<br>Design Check: PLL Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 143<br>143<br>147<br>147<br>148<br>148<br>150                                                                                                                                                                         |

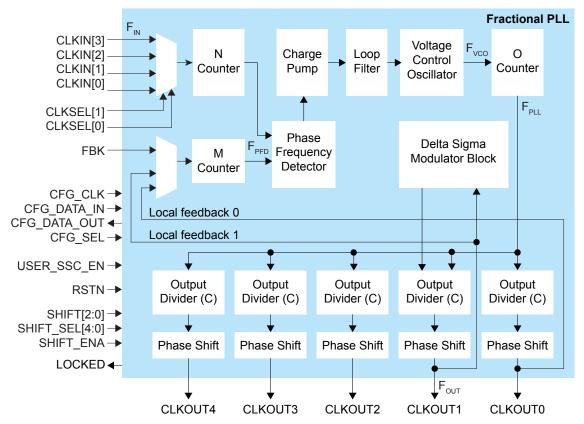

| Chapter 11: PLL Interface<br>About the PLL Interface<br>Using the PLL Block<br>Using the PLL Clock Calculator<br>Manually Configuring the PLL<br>Implementing a Zero-Delay Buffer<br>Design Check: PLL Messages<br>About the Fractional PLL Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 143<br>143<br>147<br>147<br>148<br>148<br>150<br>155                                                                                                                                                                  |

| Chapter 11: PLL Interface<br>About the PLL Interface<br>Using the PLL Block<br>Using the PLL Clock Calculator<br>Manually Configuring the PLL<br>Implementing a Zero-Delay Buffer<br>Design Check: PLL Messages<br>About the Fractional PLL Interface<br>Using the Fractional PLL Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 143<br>147<br>147<br>147<br>148<br>148<br>150<br>155<br>157                                                                                                                                                           |

| Chapter 11: PLL Interface<br>About the PLL Interface<br>Using the PLL Block<br>Using the PLL Clock Calculator<br>Manually Configuring the PLL<br>Implementing a Zero-Delay Buffer<br>Design Check: PLL Messages<br>About the Fractional PLL Interface<br>Using the Fractional PLL Block<br>Using the Fractional PLL Block<br>Using the Fractional PLL Clock Calculator                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 143<br>143<br>147<br>147<br>148<br>148<br>150<br>155<br>157<br>160                                                                                                                                                    |

| Chapter 11: PLL Interface<br>About the PLL Interface<br>Using the PLL Block<br>Using the PLL Clock Calculator<br>Manually Configuring the PLL<br>Implementing a Zero-Delay Buffer<br>Design Check: PLL Messages<br>About the Fractional PLL Interface<br>Using the Fractional PLL Block<br>Using the Fractional PLL Block<br>Using the Fractional PLL Clock Calculator<br>Design Check: Fractional PLL Messages                                                                                                                                                                                                                                                                                                                                                                                                              | 143<br>147<br>147<br>147<br>148<br>148<br>150<br>155<br>157<br>160<br>161                                                                                                                                             |

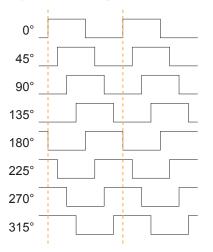

| Chapter 11: PLL Interface<br>About the PLL Interface<br>Using the PLL Block<br>Using the PLL Clock Calculator<br>Manually Configuring the PLL<br>Implementing a Zero-Delay Buffer<br>Design Check: PLL Messages<br>About the Fractional PLL Interface<br>Using the Fractional PLL Block<br>Using the Fractional PLL Block<br>Using the Fractional PLL Clock Calculator<br>Design Check: Fractional PLL Messages<br>Understanding PLL Phase Shifting                                                                                                                                                                                                                                                                                                                                                                          | 143<br>143<br>147<br>147<br>147<br>148<br>150<br>155<br>157<br>160<br>161<br>163                                                                                                                                      |

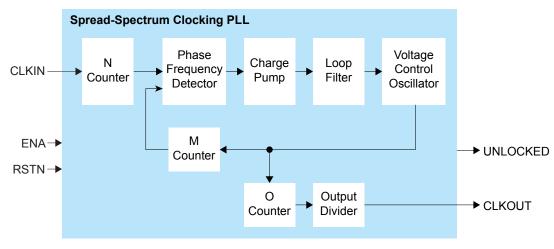

| Chapter 11: PLL Interface<br>About the PLL Interface<br>Using the PLL Block<br>Using the PLL Clock Calculator<br>Manually Configuring the PLL<br>Implementing a Zero-Delay Buffer<br>Design Check: PLL Messages<br>About the Fractional PLL Interface<br>Using the Fractional PLL Block<br>Using the Fractional PLL Block<br>Using the Fractional PLL Clock Calculator<br>Design Check: Fractional PLL Messages<br>Understanding PLL Phase Shifting<br>About the Spread-Spectrum Clocking PLL Interface                                                                                                                                                                                                                                                                                                                      | 143<br>147<br>147<br>147<br>147<br>148<br>150<br>155<br>157<br>160<br>161<br>163<br>163                                                                                                                               |

| Chapter 11: PLL Interface<br>About the PLL Interface<br>Using the PLL Block<br>Using the PLL Clock Calculator<br>Manually Configuring the PLL<br>Implementing a Zero-Delay Buffer<br>Design Check: PLL Messages<br>About the Fractional PLL Interface<br>Using the Fractional PLL Block<br>Using the Fractional PLL Block<br>Using the Fractional PLL Clock Calculator<br>Design Check: Fractional PLL Messages<br>Understanding PLL Phase Shifting                                                                                                                                                                                                                                                                                                                                                                          | 143<br>147<br>147<br>147<br>147<br>148<br>150<br>155<br>157<br>160<br>161<br>163<br>163<br>165                                                                                                                        |

| Chapter 11: PLL Interface<br>About the PLL Interface<br>Using the PLL Block<br>Using the PLL Clock Calculator<br>Manually Configuring the PLL<br>Implementing a Zero-Delay Buffer<br>Design Check: PLL Messages<br>About the Fractional PLL Interface<br>Using the Fractional PLL Block<br>Using the Fractional PLL Clock Calculator<br>Design Check: Fractional PLL Messages<br>Understanding PLL Phase Shifting<br>About the Spread-Spectrum Clocking PLL Interface<br>Using the SSC PLL Block<br>Design Check: PLL SSC Errors                                                                                                                                                                                                                                                                                             | 143<br>143<br>147<br>147<br>147<br>148<br>150<br>155<br>157<br>160<br>161<br>163<br>163<br>165<br>167                                                                                                                 |

| Chapter 11: PLL Interface         About the PLL Interface         Using the PLL Block         Using the PLL Clock Calculator         Manually Configuring the PLL         Implementing a Zero-Delay Buffer         Design Check: PLL Messages         About the Fractional PLL Interface         Using the Fractional PLL Block         Using the Fractional PLL Clock Calculator         Design Check: Fractional PLL Messages         Understanding PLL Phase Shifting         About the Spread-Spectrum Clocking PLL Interface         Using the SSC PLL Block         Design Check: PLL SSC Errors                                                                                                                                                                                                                       | 143<br>147<br>147<br>147<br>147<br>148<br>150<br>155<br>155<br>160<br>163<br>163<br>165<br>167<br>169                                                                                                                 |

| Chapter 11: PLL Interface         About the PLL Interface         Using the PLL Block         Using the PLL Clock Calculator         Manually Configuring the PLL         Implementing a Zero-Delay Buffer         Design Check: PLL Messages         About the Fractional PLL Interface         Using the Fractional PLL Block         Using the Fractional PLL Clock Calculator         Design Check: Fractional PLL Messages         Understanding PLL Phase Shifting         About the Spread-Spectrum Clocking PLL Interface         Using the SSC PLL Block         Design Check: PLL SSC Errors         Chapter 12: Oscillator         Using the Oscillator Block                                                                                                                                                     | 143<br>147<br>147<br>147<br>147<br>148<br>150<br>155<br>157<br>160<br>163<br>163<br>165<br>167<br>169                                                                                                                 |

| Chapter 11: PLL Interface         About the PLL Interface         Using the PLL Block         Using the PLL Clock Calculator         Manually Configuring the PLL         Implementing a Zero-Delay Buffer         Design Check: PLL Messages         About the Fractional PLL Interface         Using the Fractional PLL Block         Using the Fractional PLL Clock Calculator         Design Check: Fractional PLL Messages         Understanding PLL Phase Shifting         About the Spread-Spectrum Clocking PLL Interface         Using the SSC PLL Block         Design Check: PLL SSC Errors                                                                                                                                                                                                                       | 143<br>147<br>147<br>147<br>147<br>148<br>150<br>155<br>157<br>160<br>163<br>163<br>165<br>167<br>169                                                                                                                 |

| Chapter 11: PLL Interface         About the PLL Interface         Using the PLL Block         Using the PLL Clock Calculator         Manually Configuring the PLL         Implementing a Zero-Delay Buffer         Design Check: PLL Messages         About the Fractional PLL Interface         Using the Fractional PLL Block         Using the Fractional PLL Clock Calculator         Design Check: Fractional PLL Messages         Understanding PLL Phase Shifting         About the Spread-Spectrum Clocking PLL Interface         Using the SSC PLL Block         Design Check: PLL SSC Errors.         Chapter 12: Oscillator         Using the Oscillator         Using the Oscillator Block         Design Check: Oscillator Messages                                                                             | 143<br>143<br>147<br>147<br>147<br>147<br>148<br>150<br>155<br>157<br>160<br>161<br>163<br>163<br>165<br>167<br>167<br>169<br>170                                                                                     |

| Chapter 11: PLL Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 143<br>147<br>147<br>147<br>147<br>148<br>150<br>155<br>155<br>160<br>163<br>163<br>165<br>165<br>167<br>169<br>169<br>170<br>171                                                                                     |

| Chapter 11: PLL Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 143<br>147<br>147<br>147<br>147<br>148<br>150<br>155<br>157<br>160<br>163<br>163<br>165<br>167<br>169<br>169<br>169<br>180                                                                                            |

| Chapter 11: PLL Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 143<br>143<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>155<br>157<br>160<br>163<br>163<br>165<br>167<br>167<br>169<br>169<br>169<br>180<br>180<br>183                                                  |

| Chapter 11: PLL Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 143<br>143<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>148<br>155<br>157<br>160<br>163<br>163<br>165<br>167<br>169<br>169<br>180<br>180<br>183<br>186                                                         |

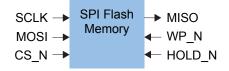

| Chapter 11: PLL Interface<br>About the PLL Interface<br>Using the PLL Block.<br>Using the PLL Clock Calculator<br>Manually Configuring the PLL.<br>Implementing a Zero-Delay Buffer<br>Design Check: PLL Messages.<br>About the Fractional PLL Interface<br>Using the Fractional PLL Block.<br>Using the Fractional PLL Clock Calculator.<br>Design Check: Fractional PLL Messages.<br>Understanding PLL Phase Shifting.<br>About the Spread-Spectrum Clocking PLL Interface.<br>Using the SSC PLL Block.<br>Design Check: PLL SSC Errors.<br>Chapter 12: Oscillator<br>Using the Oscillator Block<br>Design Check: Oscillator Messages.<br>Chapter 13: Hardened RISC-V Block Interface<br>Using the Hardened RISC-V Block<br>Design Check: RISC-V Errors.<br>Chapter 14: SPI Flash Interface<br>About the SPI Flash Memory. | 143<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>155<br>157<br>160<br>163<br>163<br>165<br>167<br>169<br>169<br>180<br>183<br>186<br>186                                           |

| Chapter 11: PLL Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 143<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>155<br>157<br>160<br>163<br>163<br>165<br>167<br>169<br>169<br>180<br>180<br>183<br>186<br>186<br>189                             |

| Chapter 11: PLL Interface<br>About the PLL Interface<br>Using the PLL Block.<br>Using the PLL Clock Calculator<br>Manually Configuring the PLL.<br>Implementing a Zero-Delay Buffer<br>Design Check: PLL Messages.<br>About the Fractional PLL Interface<br>Using the Fractional PLL Block.<br>Using the Fractional PLL Clock Calculator.<br>Design Check: Fractional PLL Messages.<br>Understanding PLL Phase Shifting.<br>About the Spread-Spectrum Clocking PLL Interface.<br>Using the SSC PLL Block.<br>Design Check: PLL SSC Errors.<br>Chapter 12: Oscillator<br>Using the Oscillator Block<br>Design Check: Oscillator Messages.<br>Chapter 13: Hardened RISC-V Block Interface<br>Using the Hardened RISC-V Block<br>Design Check: RISC-V Errors.<br>Chapter 14: SPI Flash Interface<br>About the SPI Flash Memory. | 143<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>155<br>157<br>160<br>163<br>163<br>165<br>167<br>169<br>169<br>180<br>180<br>183<br>186<br>186<br>189                             |

| Chapter 11: PLL Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 143<br>143<br>147<br>147<br>147<br>147<br>147<br>147<br>148<br>155<br>157<br>160<br>163<br>163<br>163<br>165<br>167<br>169<br>169<br>169<br>180<br>180<br>183<br>186<br>186<br>189<br>190                             |

| Chapter 11: PLL Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 143<br>143<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>147<br>155<br>157<br>160<br>163<br>163<br>165<br>167<br>169<br>169<br>169<br>169<br>180<br>180<br>183<br>186<br>186<br>189<br>190<br>191 |

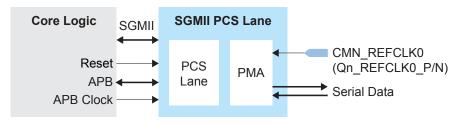

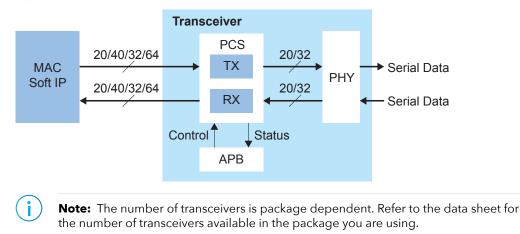

| Ethernet SGMII Control Register Tab            |     |

|------------------------------------------------|-----|

| Ethernet SGMII Pins Tab                        |     |

| Ethernet SGMII Common Properties Tab           |     |

| Using the Ethernet SGMII Interface             |     |

| Design Check: Ethernet SGMII Messages          |     |

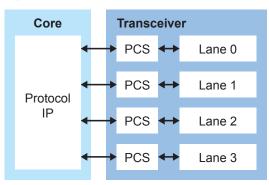

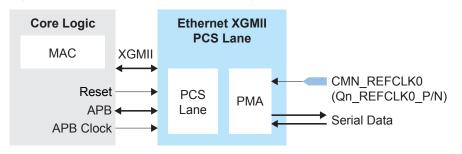

| Chapter 16: Ethernet XGMII Interface           |     |

| Ethernet XGMII Base Tab                        |     |

| Ethernet XGMII Control Register Tab            |     |

| Ethernet XGMII Pins Tab                        |     |

| Ethernet XGMII Common Properties Tab           |     |

| Using the Ethernet XGMII Interface             |     |

| Design Check: Ethernet XGMII Messages          |     |

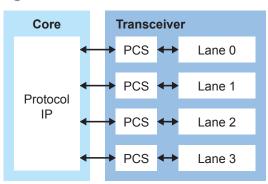

| Chapter 17: PMA Direct Interface               | 204 |

| PMA Direct Base Tab                            |     |

| PMA Direct Control Register Tab                |     |

| PMA Direct Pins Tab                            |     |

| PMA Direct Common Properties Tab               |     |

| Design Check: PMA Direct Messages              |     |

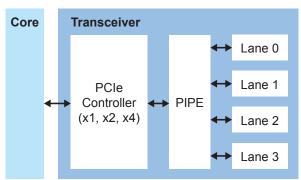

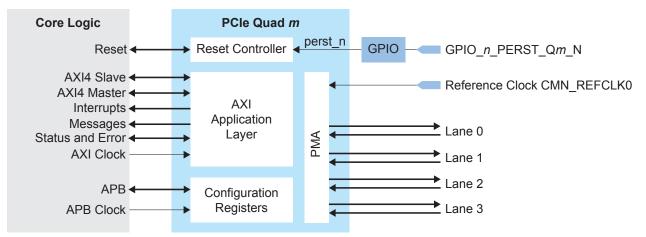

| Chapter 18: PCI Express <sup>®</sup> Interface | 214 |

| PCI Express Base Tab                           |     |

| PCI Express Reset Tab                          |     |

| PCI Express Function Tab                       |     |

| PCI Express Device Capability Tab              |     |

| PCI Express Pins Tab                           |     |

| Using the PCI Express Interface                |     |

| GPIO Block (PERST_N)                           |     |

| Reference Clock                                |     |

| Oscillator                                     |     |

| Enable Configuration User Status Pin           |     |

| Design Check: PCI Express Messages             |     |

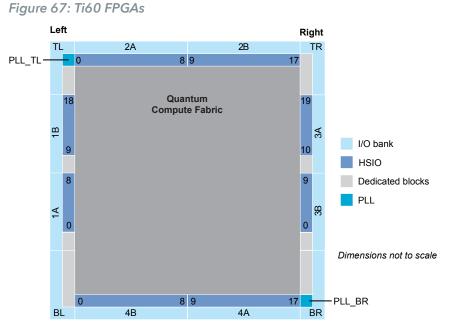

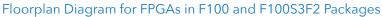

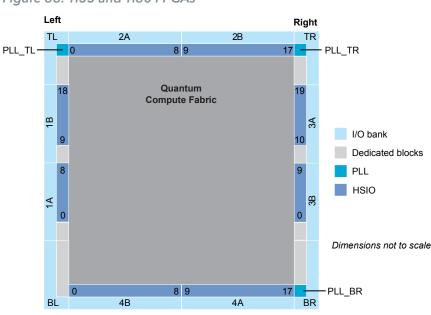

| Chapter 19: Interface Floorplans               | 227 |

| Icon Reference                                 |     |

| Revision History                               |     |

| •                                              |     |

# About the Interface Designer

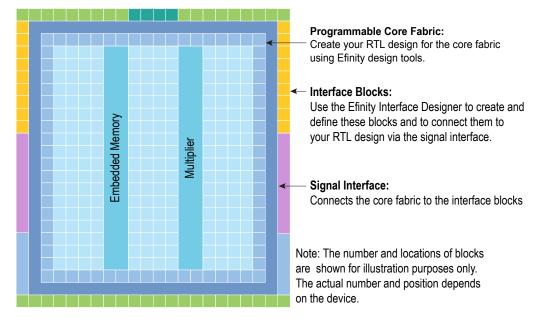

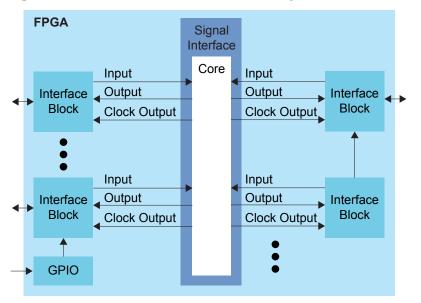

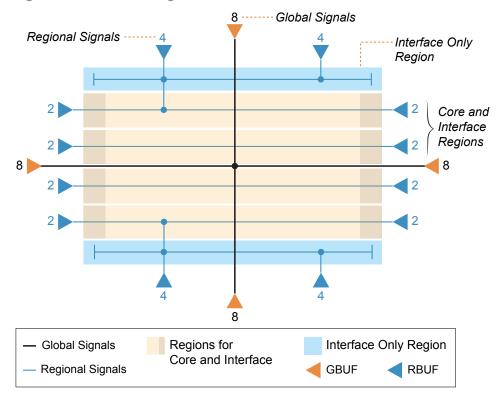

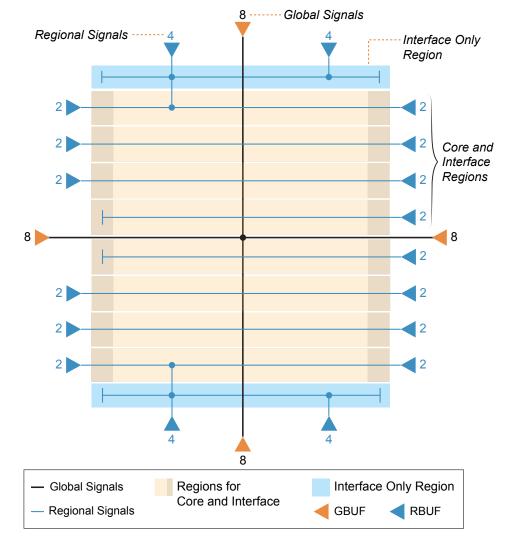

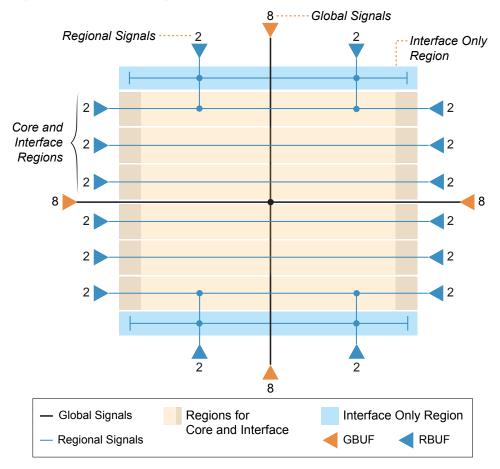

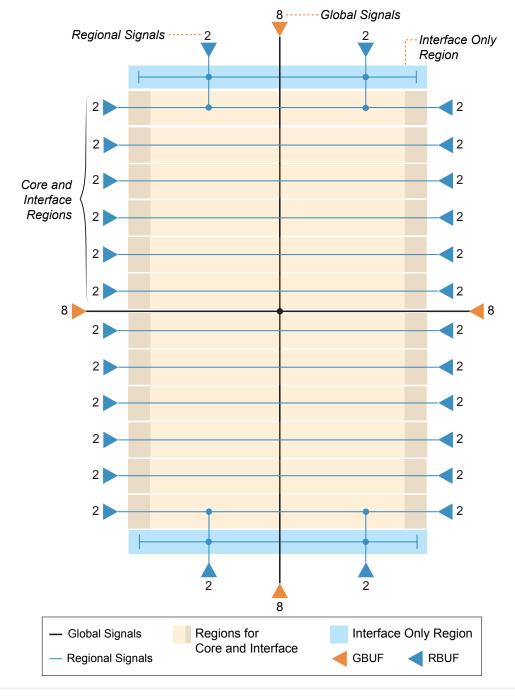

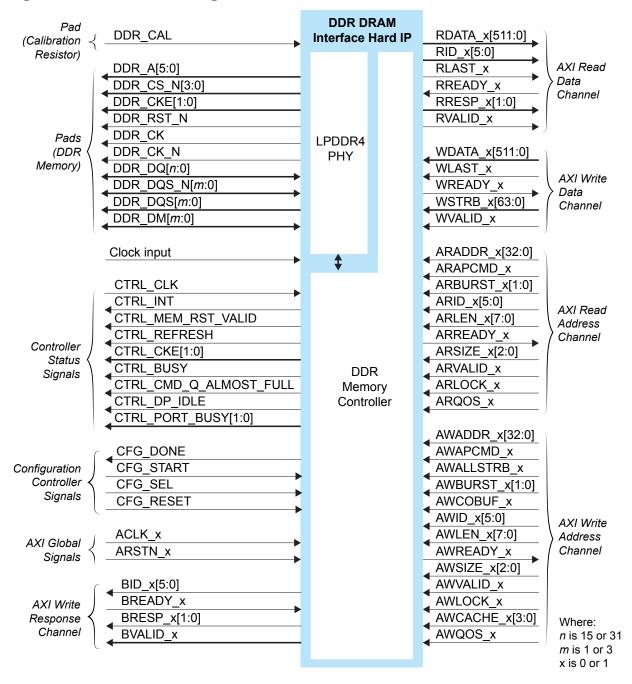

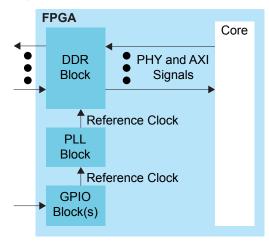

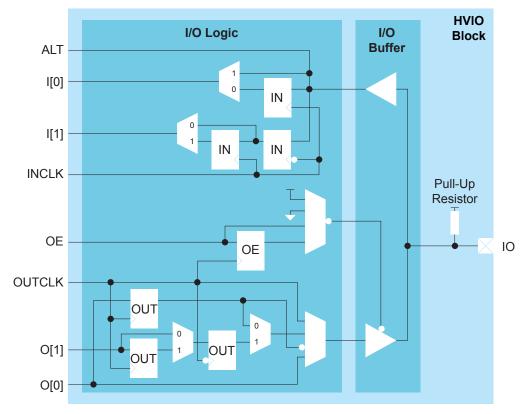

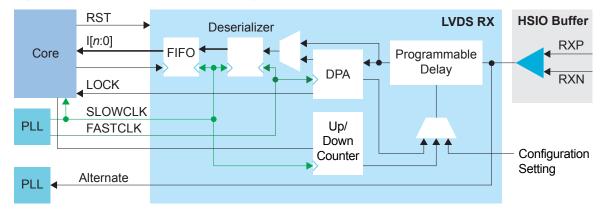

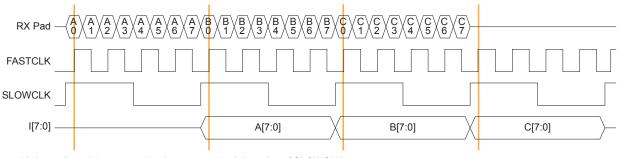

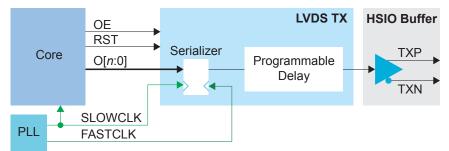

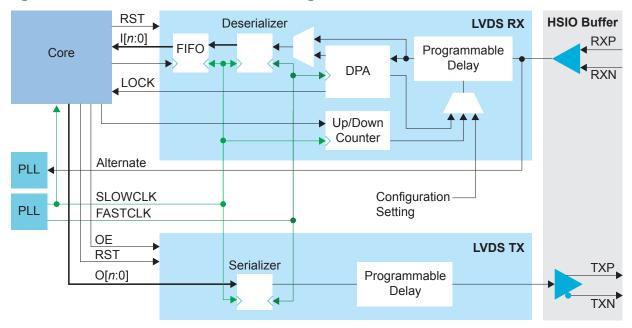

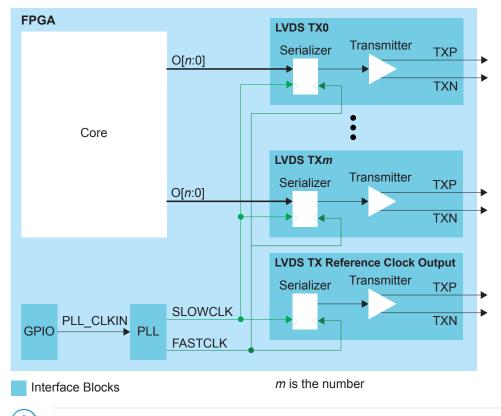

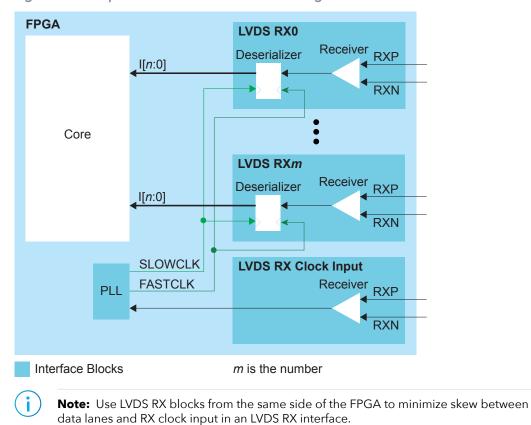

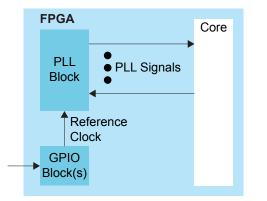

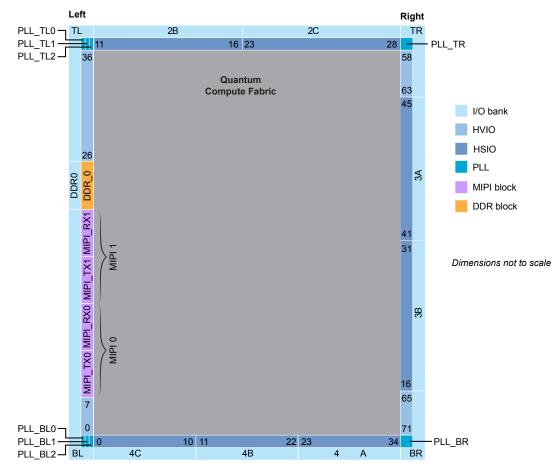

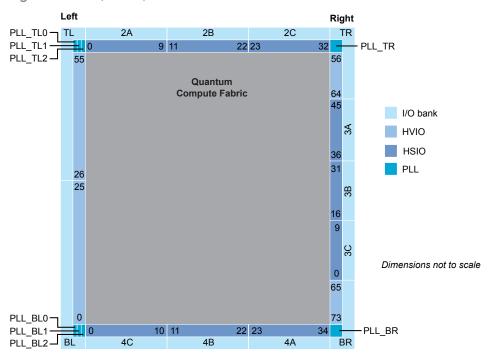

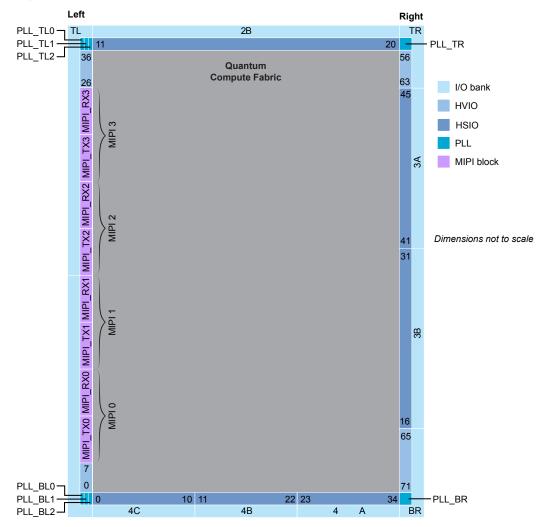

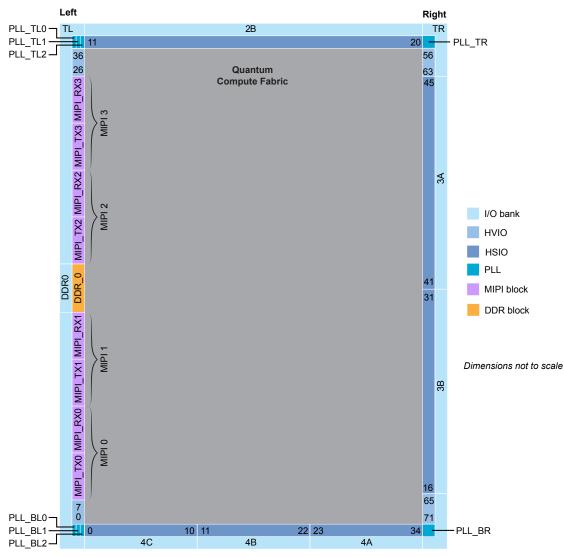

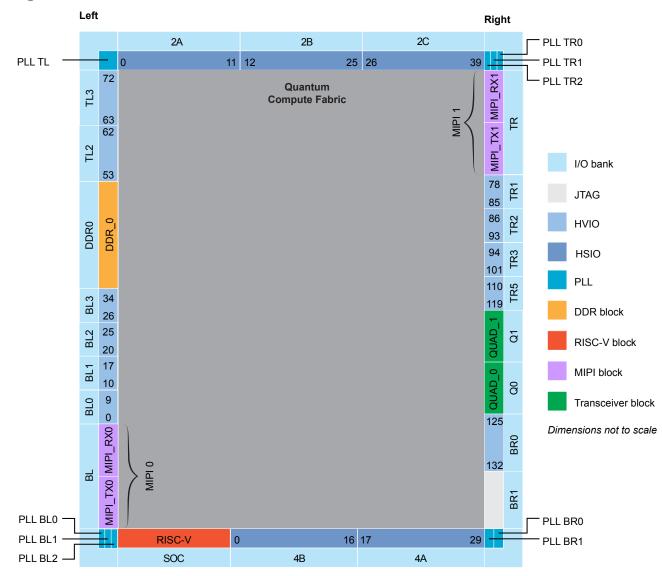

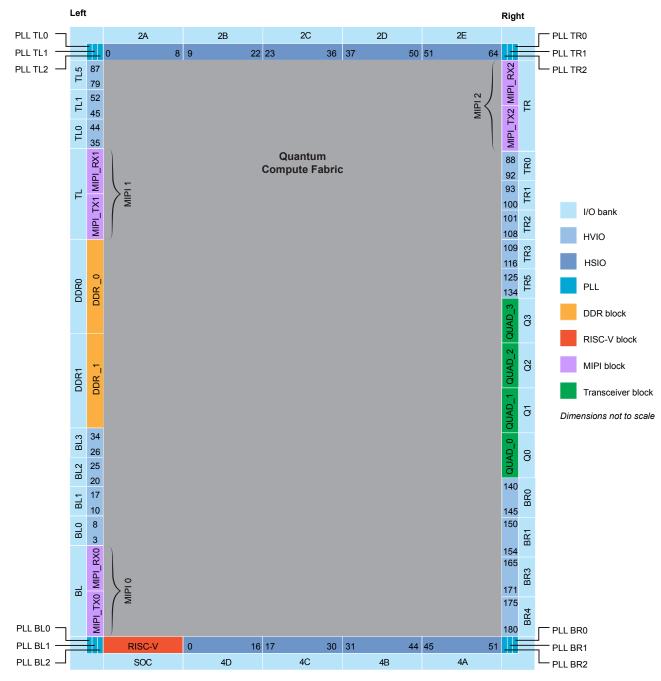

Titanium FPGAs wrap a Quantum<sup>®</sup>-accelerated core with a periphery that sends signals out to the device pins. The core contains the logic, embedded memory, and multipliers. The device periphery includes blocks such as GPIO pins, LVDS, MIPI, DDR, and PLLs.

The tools in the Efinity<sup>®</sup> main window help you design the logic portion of your design. You use the Efinity Interface Designer to build the peripheral portion of your design.

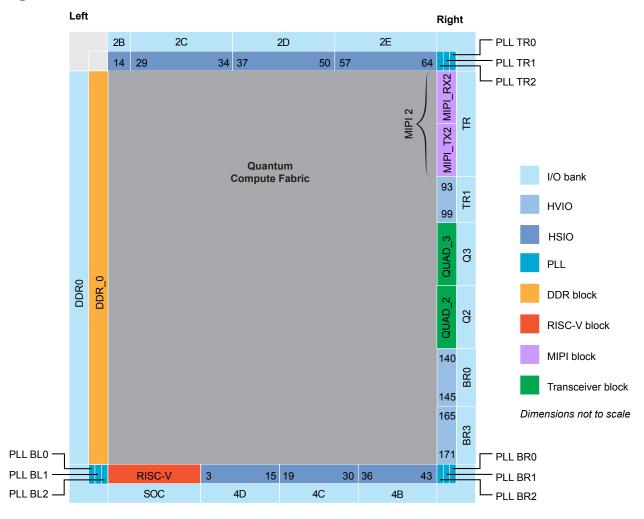

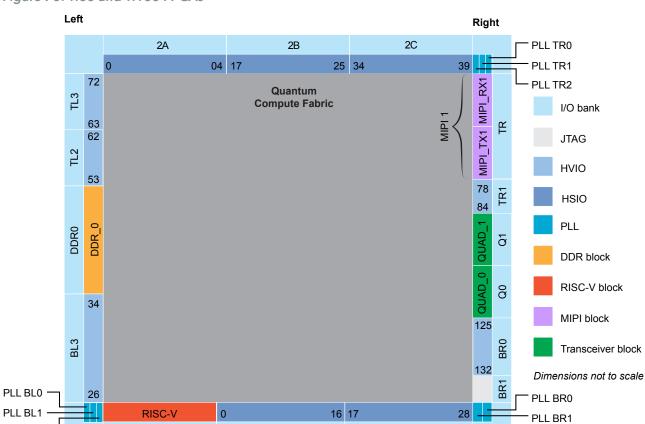

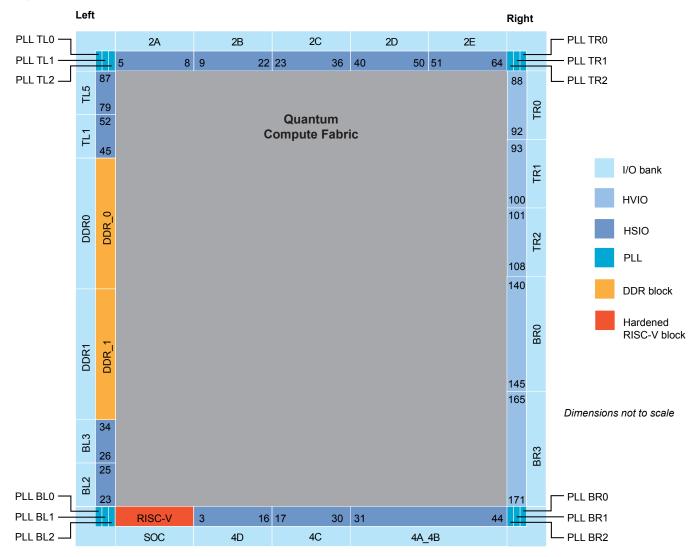

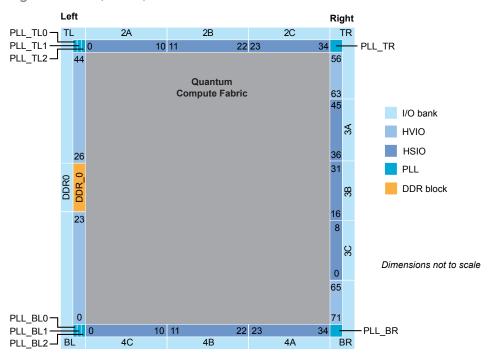

Figure 1: Conceptual View of Interface Blocks

#### Chapter 1

# Get Oriented

### **Contents:**

- Interface Blocks

- Package/Interface Support Matrix

- Interface Block Connectivity

- Clocking Interface Blocks

- Designing an Interface

- Create or Delete a Block

- Using the Resource Assigner

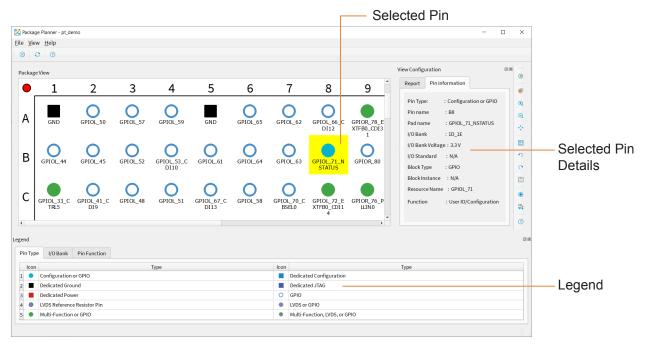

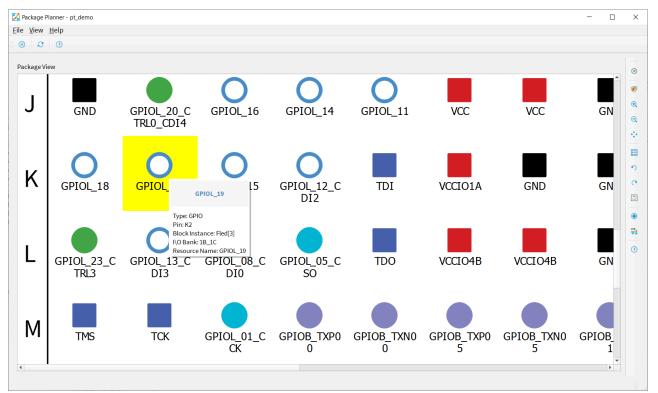

- Viewing the Package Pinout

- Interface Designer Output Files

- Scripting an Interface Design

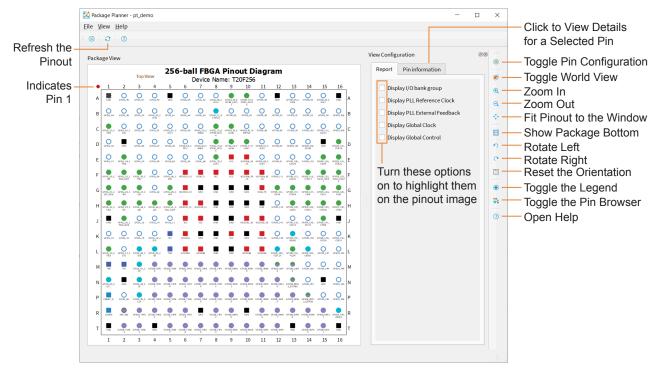

The Interface Designer has four main sections:

- *Design Explorer*—Provides a list view of the interface blocks you have in your design organized by block type. It also includes device-wide settings for the I/O banks and configuration options. Select a block to display it's summary and editor.

- *Block Summary*—Displays the current settings for the selected block.

- *Block Editor*—Provides options and settings for the selected block. The editor may have more than one tab, depending on the block.

- *Resource Assigner*—Provides an easy, tabular method for assigning resources. View by instance (default) or resource.

### Figure 2: Interface Designer

| 🖌 Ef      | inity Interface Designer - pt_demo                                                |     |                      |                      | -                                       |   |

|-----------|-----------------------------------------------------------------------------------|-----|----------------------|----------------------|-----------------------------------------|---|

| File      | Design Help 4                                                                     | 5   | 10                   |                      |                                         |   |

| $\otimes$ |                                                                                   |     |                      |                      |                                         |   |

|           | Design Explorer                                                                   | Blo | ck Summary 2         |                      | Block Editor 3                          | Ø |

|           | Type and press Enter to search                                                    |     | Property             | Value                | Oclk_out                                | 0 |

|           | Search filter                                                                     | 1   | Instance Name        | Oclk_out             | Mode                                    | _ |

| <^⁺       |                                                                                   | 2   | GPIO Resource        | GPIOR_13             | clkout                                  | - |

| Ľ         | <ul> <li>Design : T8F81</li> <li>Device Setting</li> <li>I/O Banks (5)</li> </ul> | 3   | Mode                 | clkout               | I/O Standard                            |   |

| Q         | ✓ GPIO (15)                                                                       | 4   | I/O Standard         | 3.3 V LVTTL / LVCMOS | 3.3 V LVTTL / LVCMOS                    | Ŧ |

| à         | <ul> <li>Fled [3:0]</li> <li>Oled [3:0]</li> </ul>                                | 5   | Unused State         | NA                   | Output                                  |   |

|           | ► Sled [3:0]                                                                      | 6   | Alternate Connection | None                 | Pin Name                                |   |

| ┛         | Oclk_out: GPIOR_13     D pll_clkin: GPIOL_20     G sector (CDIOL_20)              | 7   | Features             | None                 |                                         |   |

|           | resetn : GPIOL_13 PLL (1)                                                         | 8   | Clock Region         | R1                   |                                         |   |

|           | <ul> <li>Oscillator (1)</li> </ul>                                                |     | I/O Bank             | 2A                   | Constant Output                         |   |

|           | JTAG User Tap (0)                                                                 | _   |                      |                      | none                                    | - |

|           |                                                                                   | 10  | Pad                  | GPIOR_13             | Register Option                         |   |

|           |                                                                                   | 11  | Package Pin          | D6                   | none                                    |   |

|           |                                                                                   | 12  | Clkout Output        |                      |                                         |   |

|           |                                                                                   | 13  | Clock Pin Name       | Oclk                 | Drive Strength (1-weakest, 4-strongest) |   |

|           |                                                                                   | 14  | Clock Is Inverted    | false                | 1                                       |   |

|           |                                                                                   | 15  | Drive Strength       | 1                    | Enable Slew Rate                        |   |

|           |                                                                                   |     |                      |                      | Output Clock                            |   |

Notes:

- 1. The Design Explorer shows the interface blocks in your design. They are organized by block type.

- 2. The block summary shows the settings for the block selected in the Design Explorer.

- 3. Use the Block Editor to add or change settings for the interface block.

- 4. You can import or export GPIO resource assignments using a .csv or .isf file.

- 5. Use the project management tools to perform design checks, view reports, generate constraints, etc.

- 6. Click Show/Hide Resource Assigner to toggle a tabular view of assignments.

- 7. Use the block tools to add or delete blocks and buses.

- 8. Expand or collapse the Design Explorer folders.

- 9. The number in parentheses shows the number of used blocks.

- 10. The Package Planner lets you see the pins and assignments graphically.

When you first open the Interface Designer for your project, the Design Explorer shows the Device Settings folder (with default settings) and empty folders for the interface blocks your chosen device supports. You need to add blocks as required for your design.

### Figure 3: Resource Assigner

| -         | nity Interface Design         | nei pr_uenio                    |                 |     |                   |          |               |              | - [           | 1  |

|-----------|-------------------------------|---------------------------------|-----------------|-----|-------------------|----------|---------------|--------------|---------------|----|

| File      | Design Help                   |                                 |                 |     |                   |          |               |              |               |    |

| $\otimes$ | R 6 8                         | V 🗗 💀 🤇                         | D               |     |                   |          |               |              |               |    |

|           | Resource Assigner             |                                 |                 |     |                   |          |               |              |               |    |

| •         | 7 7 o i                       |                                 |                 |     |                   |          |               |              |               |    |

|           |                               |                                 | 4               |     |                   |          |               |              |               |    |

| <^+       | GPIO : Instance V             | iew                             |                 |     |                   |          |               |              |               |    |

| ď         | 5                             |                                 |                 | all | all               |          | all           | all          |               |    |

| Q         | Instance                      | <ul> <li>Package Pin</li> </ul> | Resource        |     | I/O Bank          | Alt Conn | Features      | Clock Region | Pad           |    |

| ē         |                               | J2                              | GPIOL_09        | 1A  | Non               | e        | None          | LO           | GPIOL_09_CDI2 | 2  |

| a         | Fled[1]                       | C2 3                            | GPIOL_16        | 1B  | GCL               | к        | None          | L1           | GPIOL_16_CLK  | 2  |

|           | Fled[2]                       | F8                              | GPIOR_20        | 2B  | GCL               | к        | None          | R0           | GPIOR_20_CLK  | 5  |

|           | Fled[3]                       | D8                              | GPIOR_17        | 2A  | GCT               | RL       | None          | R1           | GPIOR_17_CTR  | L  |

|           | Oclk_out                      | D6                              | GPIOR_13        | 2A  | Non               | e        | None          | R1           | GPIOR_13      |    |

|           |                               | ци                              | GRIOL 02        | 1.0 | Non               | <u>م</u> | None          | 10           |               |    |

| C         | Design Explorer               | 0 8                             | Block Summary   |     |                   |          | Block Editor  |              |               | đX |

|           | Type and press Er             | nter to search                  | Propert         |     | Value             | <b></b>  | Instance Name |              |               |    |

|           | Search filter                 | ▼ 💞                             | 1 Instance Name |     | Fled[0]           | _        | Fled[0]       |              | 0             |    |