# Asymmetric Width FIFO Core User Guide

UG-CORE-ASYM-FIFO-v1.0 July 2021 www.efinixinc.com

Copyright © 2021. All rights reserved. Efinix, the Efinix logo, the Titanium logo, Quantum, Trion, and Efinity are trademarks of Efinix, Inc. All other trademarks and service marks are the property of their respective owners. All specifications subject to change without notice.

# Contents

| Introduction                                                                                                                                                                                                           |   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Features                                                                                                                                                                                                               | 3 |

| Functional Description<br>Ports<br>Synchronous FIFO Operation<br>Asynchronous FIFO Operation<br>Asymmetric Width Operation<br>Programmable Full and Empty Signals<br>Reset<br>Datacount<br>Latency<br>Synchronous FIFO |   |

| Asynchronous FIFO<br>Customizing the Asymmetric Width FIFO<br>Asymmetric Width FIFO Testbench                                                                                                                          |   |

| Revision History                                                                                                                                                                                                       |   |

# Introduction

The Asymmetric Width FIFO core is a customizable first-in first-out memory queue that uses block RAM in the FPGA for storage. The core has parameters you use to create a custom instance. For example, you can set the FIFO depth, the data bus width, whether the read and write domains are synchronous or asynchronous, etc.

# Features

- Depths up to 131,072 words

- Data widths from 1 to 1024 bits

- Symmetric or non-symmetric aspect ratios (read-to-write port ratios ranging from 1:16 to 16:1)

- Synchronous or asynchronous clock domains supports standard

- Programmable full and empty status flags, set by user-defined parameters

- Almost full and almost empty flags indicate one word left

- Configurable handshake signals

- FIFO datacount to indicate how many words available in FIFO

- Option to exclude optional flags

- Verilog RTL and simulation testbench

#### **FPGA** Support

The Asymmetric Width FIFO core supports all Trion<sup>®</sup> and Titanium FPGAs.

#### Titanium Resource Utilization and Performance

**Note:** This is an early access version of the IP core. The resources utilization and performance of this version is not fully optimized.

| FPGA         | Asymmetric<br>Width | XLR | Memory<br>Blocks | DSP48 Blocks | f <sub>MAX</sub> (MHz)<br>- clk_i | Efinity Version |

|--------------|---------------------|-----|------------------|--------------|-----------------------------------|-----------------|

| Ti60 F225 ES | 0                   | 160 | 2                | 0            | 422                               | 2021.1          |

|              | 1                   | 152 | 2                | 0            | 440                               | ]               |

|              | 2                   | 150 | 2                | 0            | 377                               |                 |

|              | 3                   | 136 | 2                | 0            | 433                               |                 |

|              | 4                   | 60  | 2                | 0            | 474                               |                 |

|              | 5                   | 56  | 4                | 0            | 497                               |                 |

|              | 6                   | 55  | 10               | 0            | 501                               | -               |

|              | 7                   | 52  | 20               | 0            | 539                               |                 |

|              | 8                   | 50  | 32               | 0            | 501                               |                 |

#### Table 1: Synchronous Clock FIFO

i

#### Asymmetric FPGA Memory DSP48 XLR f<sub>MAX</sub> (MHz) Efinity Width Blocks Version Blocks wr\_clk\_i rd\_clk\_i Ti60 F225 2021.1 ES

#### Table 2: Asynchronous Clock FIFO

### Trion Resource Utilization and Performance

| FPGA       | Asymmetric<br>Width | Logic<br>Utilization<br>(LUTs) | Memory<br>Blocks | Multipliers | f <sub>MAX</sub> (MHz)<br>- clk_i | Efinity Version |

|------------|---------------------|--------------------------------|------------------|-------------|-----------------------------------|-----------------|

| T20 BGA256 | 0                   | 161                            | 4                | 0           | 134                               | 2021.1          |

|            | 1                   | 161                            | 4                | 0           | 134                               |                 |

|            | 2                   | 157                            | 4                | 0           | 140                               |                 |

|            | 3                   | 162                            | 4                | 0           | 144                               |                 |

|            | 4                   | 70                             | 4                | 0           | 180                               |                 |

|            | 5                   | 57                             | 4                | 0           | 172                               |                 |

|            | 6                   | 54                             | 8                | 0           | 176                               |                 |

|            | 7                   | 52                             | 20               | 0           | 168                               |                 |

|            | 8                   | 47                             | 32               | 0           | 165                               |                 |

| FPGA   | Asymmetric |     |        | Multipliers | f <sub>MAX</sub> ( | MHz)     | Efinity |

|--------|------------|-----|--------|-------------|--------------------|----------|---------|

| Width  | Width      |     | Blocks |             | wr_clk_i           | rd_clk_i | Version |

| T20    | 0          | 255 | 4      | 0           | 110                | 110      | 2021.1  |

| BGA256 | 1          | 249 | 4      | 0           | 110                | 110      |         |

|        | 2          | 250 | 4      | 0           | 118                | 118      |         |

|        | 3          | 250 | 4      | 0           | 110                | 110      |         |

|        | 4          | 153 | 4      | 0           | 132                | 132      |         |

|        | 5          | 141 | 4      | 0           | 134                | 123      |         |

|        | 6          | 128 | 8      | 0           | 138                | 134      |         |

|        | 7          | 116 | 20     | 0           | 133                | 146      | 1       |

|        | 8          | 104 | 32     | 0           | 131                | 131      | 1       |

# **Functional Description**

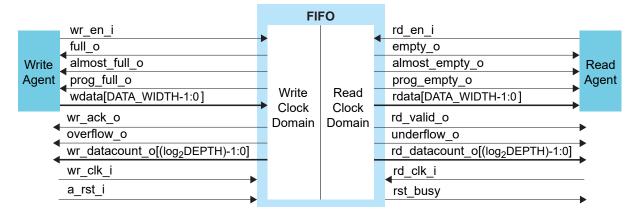

The Asymmetric Width FIFO core is a first-in first-out memory queue for any application requiring an ordered storage buffer and retrieval. The core provides an optimized solution using the block RAM in Trion<sup>®</sup> and Titanium FPGAs. The core supports synchronous (read and write use the same clock) and asynchronous (read and write use different clocks) clocking.

Figure 1: FIFO System Block Diagram

### Ports

Table 3: Asymmetric Width FIFO Core Clock, Reset and Datacount Ports

| Port                            | Synchronous  | Asynchronous | Direction | Description                                                                                     |

|---------------------------------|--------------|--------------|-----------|-------------------------------------------------------------------------------------------------|

| a_rst_i                         | $\checkmark$ | ~            | Input     | Reset. Asynchronous reset signal that<br>initializes all internal pointers and<br>output flags. |

| rst_busy                        |              | ~            | Output    | When asserted, this signal indicate the core is being reset.                                    |

| wr_clk_i                        |              | ~            | Input     | Write clock. All signals in the write domain are synchronous to this clock.                     |

| rd_clk_i                        |              | ~            | Input     | Read clock. All signals in the read domain are synchronous to this clock.                       |

| clk_i                           | ~            |              | Input     | Clock. All signals on the write and read domains are synchronous to this clock.                 |

| wr_datacount_o [ <i>n-</i> 1:0] |              | ~            | Output    | Asynchronous FIFO write domain data count.<br>n=log <sub>2</sub> [DEPTH].                       |

| rd_datacount_o [ <i>n</i> -1:0] |              | ~            | Output    | Asynchronous FIFO read domain data count.<br>n=log2[DEPTH].                                     |

| datacount_o [ <i>n</i> -1:0]    | $\checkmark$ |              | Output    | Synchronous FIFO data count.<br>n=log <sub>2</sub> [DEPTH].                                     |

#### Table 4: Asymmetric Width FIFO Core Write Ports

| Port                   | Direction | Description                                                                                                                                                                                                                                   |

|------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| wdata [ <i>m</i> -1:0] | Input     | Write data. The input data bus used when writing to the FIFO buffer.<br><i>m</i> =DATA_WIDTH.                                                                                                                                                 |

| wr_en_i                | Input     | Write enable. If the FIFO buffer is not full, asserting this signal causes data (on wdata) to be written to the FIFO.                                                                                                                         |

| full_o                 | Output    | Full flag. When asserted, this signal indicates that the FIFO buffer is full.<br>Write requests are ignored when the FIFO is full. Initiating a write while full<br>is not destructive to the FIFO.                                           |

| almost_full_o          | Output    | Optional, almost full. When asserted, this signal indicates that only one more write can be performed before the FIFO is full.                                                                                                                |

| prog_full_o            | Output    | Optional, programmable full. This signal is asserted when the number<br>of words in the FIFO is greater than or equal to the assert threshold. It is<br>deasserted when the number of words in the FIFO is less than the negate<br>threshold. |

| wr_ack_o               | Output    | Optional, write acknowledge. This signal indicates that a write request (wr_en_i) during the prior clock cycle succeeded.                                                                                                                     |

| overflow_o             | Output    | Optional, overflow. This signal indicates that a write request (wr_en_i) during the prior clock cycle was rejected because the FIFO buffer is full. Overflowing the FIFO is not destructive to the contents of the FIFO.                      |

For both synchronous and asynchronous clocks.

#### Table 5: Asymmetric Width FIFO Core Read Ports

For both synchronous and asynchronous clocks.

| Port                   | Direction | Description                                                                                                                                                                                                                                    |

|------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rdata [ <i>m</i> -1:0] | Output    | Read data. The output data bus driven when reading the FIFO buffer.<br>m=DATA_WIDTH.                                                                                                                                                           |

| rd_en_i                | Input     | Read enable. If the FIFO buffer is not empty, asserting this signal causes data to be read from the FIFO (output on rdata).                                                                                                                    |

| empty_o                | Output    | Empty flag. When asserted, this signal indicates that the FIFO buffer is empty. When empty, Read requests are ignored. Initiating a read while empty is not destructive to the FIFO.                                                           |

| almost_empty_o         | Output    | Optional, almost empty flag. When asserted, this signal indicates that only one word remains in the FIFO buffer before it is empty.                                                                                                            |

| prog_empty_o           | Output    | Optional, programmable empty. This signal is asserted when the number<br>of words in the FIFO buffer is less than or equal to the assert threshold. It<br>is de-asserted when the number of words in the FIFO exceeds the negate<br>threshold. |

| rd_valid_o             | Output    | Optional, read valid. This signal indicates that valid data is available on the output bus (rdata).                                                                                                                                            |

| underflow_o            | Output    | Optional, underflow. Indicates that the read request (rd_en_i) during<br>the previous clock cycle was rejected because the FIFO buffer is empty.<br>Underflowing the FIFO is not destructive to the FIFO.                                      |

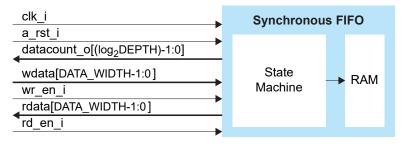

# Synchronous FIFO Operation

The FIFO core signals are synchronized on the rising edge clock of the respective clock domain. If you want to synchronize to the falling clock edge, use an inverter before sending the signal to the clock input.

Figure 2: Synchronous FIFO Block Diagram

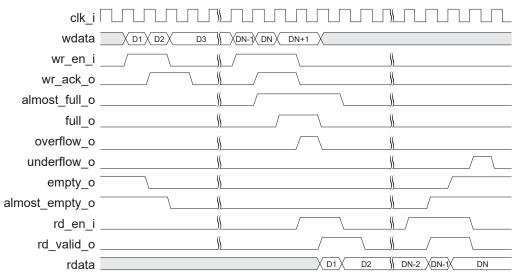

#### Standard Mode

The following waveform shows the FIFO behavior in standard mode when it is written until full and then read until empty. D1 and DN are the first and last data, respectively.

If the system tries to write data DN+1 when full\_o is asserted, the core ignores DN+1 and asserts overflow\_o. full\_o deasserts during a read request, signaling that the FIFO is ready for more write requests. When the last data is read from the FIFO, the core asserts empty\_o, indicating there is no more data. Further read requests when there is no more data triggers an assertion on underflow o.

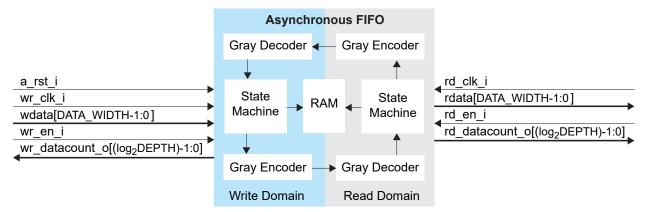

# Asynchronous FIFO Operation

With an asynchronous FIFO, the two protocols can work in their respective clock domains and still transfer reliable data to each other. When there is a write or read request affecting its own respective domain's flags, the asynchronous FIFO has 0 delays. Whereas when affecting the other domain's flags, it has a 1 clock cycle delay from its respective domain plus 2 clock cycles of the other domain. For example, a write request only reflects on the read domain after 1 write clock cycle plus 2 read clock cycles and vice versa. Enabling the PIPELINE\_REGadds 1 more additional clock cycle of the other domain on top of it. Refer to the latency table for asynchronous FIFO in Latency on page 13 for more info.

For asynchronous FIFO, a write operation affecting the write domain flags and a read operation affecting the read domain flags have the same behavior as the synchronous FIFO except when they are affecting crossed domain flags. The following examples emphasize the cross-clock domain flags update latency.

#### Standard Mode

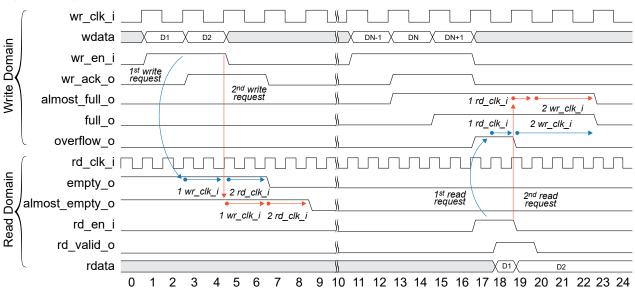

The following figures show examples of asynchronous FIFO standard mode with a faster read clock and write clock, respectively. The waveforms show the FIFO written until full and a few read requests afterwards.

In the read example shown in Figure 5: Asynchronous FIFO Standard Mode Faster Read Clock with PIPELINE\_REG=0 on page 9, the read clock frequency is double that of the write clock with the same phase. When there is a write request at node 2, empty\_o does not deassert immediately; instead, it deasserts 1 write clock plus 2 clock read clocks later at node 6. Similarly, almost\_empty\_o deasserts at node 8, which is 1 write clock plus 2 read clocks later after the second write request at node 4. almost\_full\_o and full\_o deassert at the same time at node 22 because there are 2 read requests detected before the write domain is synchronized at node 20.

Figure 5: Asynchronous FIFO Standard Mode Faster Read Clock with PIPELINE\_REG=0

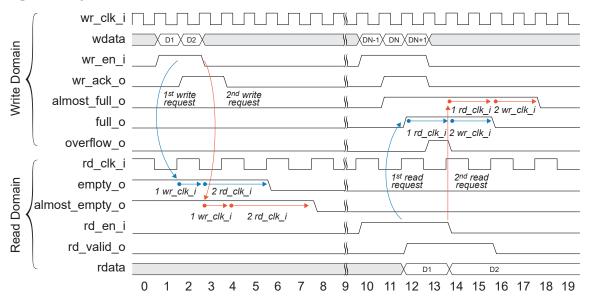

In the write example shown in Figure 6: Asynchronous FIFO Standard Mode Faster Write Clock with PIPELINE\_REG=0 on page 9, the write clock frequency is double that of the read clock with the same phase. The empty\_0 deasserts at node 5 and almost\_empty\_0 deasserts at node 7. Each of these signals are affected by write requests on node 1 and node 2 respectively. Read requests at node 11 and 13 reflect on the write domain at node 15 and 17, respectively.

Figure 6: Asynchronous FIFO Standard Mode Faster Write Clock with PIPELINE\_REG=0

# Asymmetric Width Operation

Asymmetric aspect ratios allow the input and output of the FIFO width and depth to be configured in differently. You only need to configure the write width and depth, while the read width and read depth are be computed automatically by the Asymmetric Width FIFO based on your parameter settings. The following table lists the supported asymmetric width ratio.

| Ratio | Write Width | Read Width | Write Depth    | Read Depth          |

|-------|-------------|------------|----------------|---------------------|

| 16:1  | N           | N/16       | 2 <sup>M</sup> | 2 <sup>M</sup> x 16 |

| 8:1   | N           | N/8        | 2 <sup>M</sup> | 2 <sup>M</sup> x 8  |

| 4:1   | N           | N/4        | 2 <sup>M</sup> | 2 <sup>M</sup> x 4  |

| 2:1   | N           | N/2        | 2 <sup>M</sup> | 2 <sup>M</sup> x 2  |

| 1:1   | N           | N          | 2 <sup>M</sup> | 2 <sup>M</sup>      |

| 1:2   | N           | N*2        | 2 <sup>M</sup> | 2 <sup>M</sup> / 2  |

| 1:4   | N           | N*4        | 2 <sup>M</sup> | 2 <sup>M</sup> / 4  |

| 1:8   | N           | N*8        | 2 <sup>M</sup> | 2 <sup>M</sup> / 8  |

| 1:16  | N           | N*16       | 2 <sup>M</sup> | 2 <sup>M</sup> / 16 |

Table 6: Supported Asymmetric Width FIFO Ratio

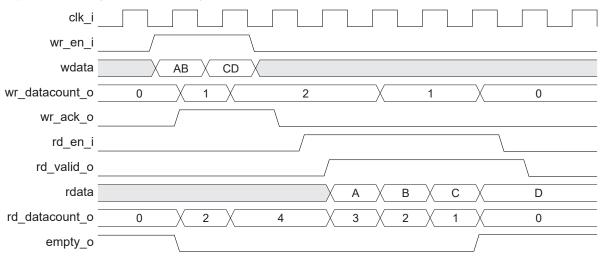

In operations with 2:1 aspect ratio, the write width is two times the read width. In the example below, each write request has 8-bit data which requires 2 read requests (4-bit width per clock cycle) to free-up the entry.

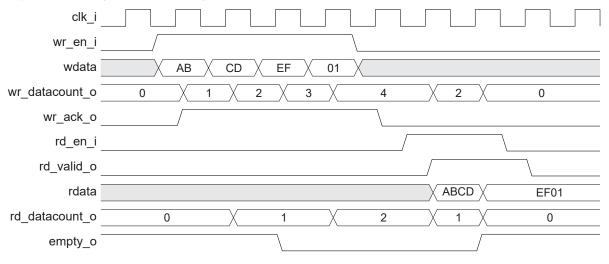

In operations with 1:2 aspect ratio, the read width is two times the write width. In the example below, each write request has 8-bit data where two write requests are required to contribute to a single read word (16-bit width).

### Programmable Full and Empty Signals

The FIFO core supports user-defined full and empty signals with customized depths (prog\_full\_o and prog\_empty\_o). To enable these signals, set the PROGRAMMABLE\_FULL or PROGRAMMABLE\_EMPTY parameters as STATIC\_SINGLE or STATIC\_DUAL. Refer to Parameters for more info on the available values.

**Important:** For the asynchronous FIFO, these signals are synchronized to their respective clock domain's available words.

#### Table 7: prog\_full\_o Assert and Deassert Conditions

| Value         | Туре     | Condition                                       |

|---------------|----------|-------------------------------------------------|

| STATIC_SINGLE | Assert   | number of words in FIFO $\geq$ PROG_FULL_ASSERT |

|               | Deassert | number of words in FIFO < PROG_FULL_ASSERT      |

| STATIC_DUAL   | Assert   | number of words in FIFO $\geq$ PROG_FULL_ASSERT |

|               | Deassert | number of words in FIFO < PROG_FULL_NEGATE      |

#### Table 8: prog\_empty\_o Assert and Deassert Conditions

| Value         | Туре     | Condition                                   |

|---------------|----------|---------------------------------------------|

| STATIC_SINGLE | Assert   | number of words in FIFO < PROG_EMPTY_ASSERT |

|               | Deassert | number of words in FIFO > PROG_EMPTY_ASSERT |

| STATIC_DUAL   | Assert   | number of words in FIFO < PROG_EMPTY_ASSERT |

|               | Deassert | number of words in FIFO > PROG_EMPTY_NEGATE |

To avoid erratic behavior, follow these rules for STATIC\_DUAL modes:

- PROG\_FULL\_ASSERT ≥ PROG\_FULL\_NEGATE

- PROG\_EMPTY\_ASSERT ≤ PROG\_EMPTY\_NEGATE

### Reset

The Asymmetric Width FIFO core can be reset through the a\_rst\_i reset signal, which is active high. In synchronous mode, the FIFO operation can be started as soon as 3 cycles after the reset signal go low. For asynchronous mode, the FIFO operation only can be started after the reset\_busy signal go low. Ensure that the reset pulse is equivalent or more than 2 clock cycles of the slowest clock

### Datacount

i.

The FIFO core includes datacount signal as output. Synchronous FIFO enables datacount\_o while asynchronous FIFO enables both wr\_datacount\_o and rd datacount\_o.

The datacount is zero when the FIFO is in empty and full state. You must ensure that the width of datacount is log<sub>2</sub>(DEPTH) to get the correct value.

Note: Always refer to the empty\_o and full\_o signals when reading or writing FIFO.

# Latency

This section defines the latency of the output signals in the FIFO core. The output signals latency are updated in response to the read or write requests. Latency is described in the following waveform. A 0 latency means the signal is asserted or deasserted at the same rising edge of the clock at which the write or read request is sampled. A latency of 1 means the signal is asserted or deasserted at the next rising edge of the clock.

### Synchronous FIFO

Table 9: Synchronous FIFO Write Flags Update Latency (clk\_i) Due to wr\_en\_i and rd\_en\_i Signals

| Port          | wr_en_i | rd_en_i |

|---------------|---------|---------|

| wr_ack_o      | 0       | -       |

| full_o        | 0       | 0       |

| almost_full_o | 0       | 0       |

| prog_full_o   | 0       | 0       |

| overflow_o    | 0       | -       |

Table 10: Synchronous FIFO Read Flags Update Latency Due to wr\_en\_i and rd\_en\_i Signals

| Port           | wr_en_i | rd_en_i          |

|----------------|---------|------------------|

| rd_valid_o     | -       | 0 <sup>(1)</sup> |

| empty_o        | 0       | 0                |

| almost_empty_o | 0       | 0                |

| prog_empty_o   | 0       | 0                |

| underflow_o    | -       | 0                |

| datacount_o    | 0       | 0                |

### Asynchronous FIFO

| Table 11: Asynchronous | FIFO Write Flags Update | Latency Due to wr_en_i |

|------------------------|-------------------------|------------------------|

|------------------------|-------------------------|------------------------|

| Port           | Latency (PIPELINE_REG=0) | Latency (PIPELINE_REG=1) |

|----------------|--------------------------|--------------------------|

| wr_ack_o       | 0                        | 0                        |

| full_o         | 0                        | 0                        |

| almost_full_o  | 0                        | 0                        |

| prog_full_o    | 0                        | 0                        |

| overflow_o     | 0                        | 0                        |

| wr_datacount_o | 0                        | 0                        |

<sup>&</sup>lt;sup>(1)</sup> OUTPUT\_REG adds one latency to these signal.

| Port           | Latency (PIPELINE_REG=0) | Latency (PIPELINE_REG=1) |

|----------------|--------------------------|--------------------------|

| rd_valid_o     | -                        | -                        |

| empty_o        | 1 wr_clk_i + 2 rd_clk_i  | 1 wr_clk_i + 3 rd_clk_i  |

| almost_empty_o | 1 wr_clk_i + 2 rd_clk_i  | 1 wr_clk_i + 3 rd_clk_i  |

| prog_empty_o   | 1 wr_clk_i + 2 rd_clk_i  | 1 wr_clk_i + 3 rd_clk_i  |

| underflow_o    | -                        | -                        |

| rd_datacount_o | 1 wr_clk_i + 2 rd_clk_i  | 1 wr_clk_i + 3 rd_clk_i  |

Table 12: Asynchronous FIFO Read Flags Update Latency Due to wr\_en\_i

Table 13: Asynchronous FIFO Write Flags Update Latency Due to rd\_en\_i

| Port           | Latency (PIPELINE_REG=0) | Latency (PIPELINE_REG=1) |

|----------------|--------------------------|--------------------------|

| wr_ack_o       | -                        | -                        |

| full_o         | 1 rd_clk_i + 2 wr_clk_i  | 1 rd_clk_i + 3 wr_clk_i  |

| almost_full_o  | 1 rd_clk_i + 2 wr_clk_i  | 1 rd_clk_i + 3 wr_clk_i  |

| prog_full_o    | 1 rd_clk_i + 2 wr_clk_i  | 1 rd_clk_i + 3 wr_clk_i  |

| overflow_o     | -                        | -                        |

| wr_datacount_o | 1 rd_clk_i + 2 wr_clk_i  | 1 rd_clk_i + 3 wr_clk_i  |

Table 14: Asynchronous FIFO Read Flags Update Latency Due to rd\_en\_i

| Port           | Latency (PIPELINE_REG=0) | Latency (PIPELINE_REG=1) |

|----------------|--------------------------|--------------------------|

| rd_valid_o     | 0 <sup>(2)</sup>         | 0 <sup>(3)</sup>         |

| empty_o        | 0                        | 0                        |

| almost_empty_o | 0                        | 0                        |

| prog_empty_o   | 0                        | 0                        |

| underflow_o    | 0                        | 0                        |

| rd_datacount_o | 0                        | 0                        |

<sup>&</sup>lt;sup>(2)</sup> OUTPUT\_REG adds one latency to these signal.

<sup>(3)</sup> OUTPUT\_REG adds one latency to these signal.

# Customizing the Asymmetric Width FIFO

The core has parameters so you can customize its function. You set the parameters in the **test\_param.vh** file.

| Table 15: Asymmetric Width FIFO Core Para | meter |

|-------------------------------------------|-------|

|                                           |       |

| Parameter         | Options                                  | Description                                                                                                                                                                                                                                                                |

|-------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYNC_CLK          | Asynchronous,<br>Synchronous             | Defines whether the FIFO read and write domain is synchronous or asynchronous.<br>Default: Synchronous                                                                                                                                                                     |

| DEPTH             | 16 - 131072                              | Defines the FIFO depth, which determines the maximum number of words the FIFO can store before it is full. The depth is multiples of 2 from 16 - 2 <sup>17</sup> . Default: 512                                                                                            |

| DATA_WIDTH        | 1 - 256                                  | Defines the FIFO's read and write data bus widths.<br>Default: 32                                                                                                                                                                                                          |

| MODE              | STANDARD                                 | Defines the FIFO's read mode.<br>Default: STANDARD                                                                                                                                                                                                                         |

| OUTPUT_REG        | Enable, Disable                          | Adds one pipeline stage to rdata and rd_valid_o to improve<br>timing delay out from efx_ram.<br>Default: Enable                                                                                                                                                            |

| PROG_FULL_ASSERT  | 1 – DEPTH                                | Threshold value when prog_full_o is enabled. When Enable<br>Programmable Full Option is:<br>STATIC_SINGLE: Single threshold value for assertion and<br>deassertion of prog_full_o.<br>STATIC_DUAL: Upper threshold value for assertion of<br>prog_full_o.<br>Default: 512  |

| PROGRAMMABLE_FULL | NONE,<br>STATIC_SINGLE,<br>STATIC_DUAL   | Controls the prog_full_o signal:<br>NONE: Disabled.<br>STATIC_SINGLE: Enabled, asserts and deasserts at a single<br>threshold value. (default)<br>STATIC_DUAL: Enabled, asserts or deasserts at different<br>threshold values.                                             |

| PROG_FULL_NEGATE  | 1 -<br>Programmable<br>Full Assert Value | Use when PROGRAMMABLE_FULL is set to STATIC_DUAL. Sets the lower threshold value for prog_full_o during deassertion. Default: 512                                                                                                                                          |

| PROG_EMPTY_ASSERT | 0 - (FIFO<br>Depth-1)                    | Threshold value when prog_empty_o is enabled. When Enable<br>Programmable Full Option is:<br>STATIC_SINGLE: Single threshold value for assertion and<br>deassertion of prog_empty_o.<br>STATIC_DUAL: Lower threshold value for assertion of<br>prog_empty_o.<br>Default: 0 |

| Parameter          | Options                                           | Description                                                                                                                                                                                                                                                                                                                  |

|--------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROG_EMPTY_NEGATE  | Programmable<br>Empty Assert<br>Value - (DEPTH-1) | Use when PROGRAMMABLE_EMPTY is set to STATIC_DUAL.<br>Sets the upper threshold value for prog_empty_o during<br>deassertion.<br>Default: 0                                                                                                                                                                                   |

| PROGRAMMABLE_EMPTY | NONE,<br>STATIC_SINGLE,<br>STATIC_DUAL            | Controls the prog_empty_o signal:<br>NONE: Disabled.<br>STATIC_SINGLE: Enabled, asserts and deasserts at a single<br>threshold value. (default)<br>STATIC_DUAL: Enabled, asserts or deasserts at different<br>threshold values.                                                                                              |

| OPTIONAL_FLAGS     | Enable, Disable                                   | Enables the optional signals: wr_ack_o, almost_full_o,<br>overflow_o, rd_valid_o, almost_empty_o and underflow_o. You<br>can disable this feature to improve macro timing.<br>Default: Enable                                                                                                                                |

| PIPELINE_REG       | Enable, Disable                                   | Applicable to Asynchronous FIFO mode only. Adds one latency<br>of the opposing clock domain to all applicable output signals<br>when wr_en_i or rd_en_i signal is asserted. Enable this feature<br>to improve the macro timing. You can disable this feature if a<br>project does not require fast speed.<br>Default: Enable |

| SYNC_STAGE         | 1 - 4                                             | Number of synchronization stages in asynchronous mode.<br>Default: 2                                                                                                                                                                                                                                                         |

| ASYM_WIDTH_RATIO   | 0 - 8                                             | Selects asymmetrical width ratios:<br>0: 16:1 ratio<br>1: 8:1 ratio<br>2: 4:1 ratio<br>3: 2:1 ratio<br>4: 1:1 ratio (default)<br>5: 1:2 ratio<br>6: 1:4 ratio<br>7: 1:8 ratio<br>8: 1:16 ratio                                                                                                                               |

# Asymmetric Width FIFO Testbench

The core includes a simulation testbench, **tb.sv**, which performs asymmetric width FIFO write and FIFO read operation according to the configured asymmetric width ratio. The FIFO read data is verified during the simulation.

Refer to the **readme.txt** file in the testbench folder for detailed steps to run the simulation testbench.

The simulation run time depends on the DEPTH parameter set. The default value is 512.

# **Revision History**

#### Table 16: Revision History

| Date      | Version | Description      |

|-----------|---------|------------------|

| July 2020 | 1.0     | Initial release. |