# **Efinity**<sup>®</sup> **Timing Closure User Guide**

UG-EFN-TIMING-v5.0 December 2023 www.efinixinc.com

# **Contents**

| About Constraints                                                                  |    |

|------------------------------------------------------------------------------------|----|

| Tools for Exploring Timing                                                         |    |

| SDC File Overview                                                                  | 8  |

| About SDC Files                                                                    |    |

| Create an Empty SDC File                                                           |    |

| Add an SDC File to Your Project                                                    |    |

| Using Multiple SDC Files                                                           |    |

| Efinity Files You Use to Create Constraints                                        | 10 |

| Constraining Clocks                                                                |    |

| Defining Clocks                                                                    |    |

| Using the create_clock Constraint                                                  |    |

| Using the create_generated_clock Constraint                                        |    |

| Virtual Clocks                                                                     |    |

| Clock LatencyGPIO Clock Latency                                                    |    |

| PLL Local Feedback Clock Latency                                                   |    |

| PLL Core Feedback Clock Latency                                                    |    |

| PLL External Feedback Clock Latency                                                |    |

| PLL Cascading Clock Latency                                                        |    |

| Clock Relationships                                                                |    |

| Setting Constraints for Unrelated Clocks                                           |    |

| Using the set_clock_groups Constraint                                              | 26 |

| Using the set_false_path Constraint                                                |    |

| Clock Synchronizers                                                                |    |

| Metastable Synchronizer Circuit                                                    |    |

| How to Set Clock Uncertainty                                                       | 29 |

| Constraining I/O                                                                   |    |

| Constraining Synchronous Inputs and Outputs                                        |    |

| Constraining Unsynchronized Inputs and Outputs                                     |    |

| Input Receive Clock Delay                                                          |    |

| Output Receive Clock Delay                                                         |    |

| Input Forward Clock Delay (GPIO clkout)                                            |    |

| Output Forward Clock Delay (GPIO clkout)Input Forward Clock Delay (GPIO output)    |    |

| Output Forward Clock Delay (GPIO output)  Output Forward Clock Delay (GPIO output) |    |

|                                                                                    |    |

| Timing Exceptions  Example: Clock-to-Clock Path with Control                       |    |

| Understanding False Paths                                                          |    |

| Understanding Min and Max Delays                                                   |    |

| Understanding Multicycle Constraints                                               |    |

| Shifted Capture Window                                                             |    |

| Shifted and Widened Window                                                         |    |

| Constraints between Fast and Slow Clocks                                           |    |

| SDC Warnings                                                                       | 49 |

| Common Mistakos                                                                    | 40 |

| SDC   | Tips and Tricks                                     |    |

|-------|-----------------------------------------------------|----|

|       | SDC Syntax                                          |    |

|       | Wildcard Commands                                   |    |

|       | Regular Expressions                                 | 51 |

|       | Inverted Clocks                                     | 51 |

|       | Square Brackets in Clock Names                      |    |

| SDC   | Constraints (Alphabetical)                          | 52 |

|       | create_clock Constraint                             |    |

|       | create_generated_clock Constraint                   | 53 |

|       | get_fanouts Constraint                              | 53 |

|       | set_clock_groups Constraint                         | 54 |

|       | set_clock_latency Constraint                        | 54 |

|       | set_clock_uncertainty Constraint                    | 55 |

|       | set_false_path Constraint                           | 55 |

|       | set_input_delay and set_output_delay Constraints    | 56 |

|       | set_max_delay and set_min_delay Constraints         |    |

|       | set_multicycle_path Constraint                      |    |

|       | -through Option                                     | 58 |

|       | Constraint Object Specifiers                        | 58 |

| SDC   | Examples                                            | 50 |

| JDC   | Example: Dynamic Multiplexers and create_clock -add |    |

|       | Example: FPGA Forwarded Clock                       |    |

|       | Example: Generated Clock with Clock Multiplexer     |    |

|       | Example: Soft SERDES                                |    |

|       | Example: Disable Impossible Paths                   |    |

|       |                                                     |    |

| Inter | rpreting Timing Results                             |    |

|       | Clock Frequency Summary                             |    |

|       | Clock Relationship Summary                          |    |

|       | Critical Paths                                      | 65 |

| Cons  | straining Logic and Routing Manually (Beta)         | 67 |

|       | Tiles                                               |    |

|       | Working with Primitives                             | 69 |

|       | Enabling Manual Assignments                         | 70 |

|       | Assignment Rules                                    |    |

|       | Creating a Location Assignment File                 | 71 |

|       | Constraining Routing Manually (Beta)                | 73 |

|       | Routing Constraint Flow                             | 73 |

|       | Enabling Routing Constraints                        | 73 |

|       | Generate .rcf Template                              | 74 |

|       | Creating a Routing Constraint File                  | 74 |

|       | Best Practices for Constraining Routing             | 75 |

| Meth  | hods for Closing Timing                             | 76 |

|       | Synthesis Options                                   |    |

|       | Handling High Fanouts                               |    |

|       | Place-and-Route Options                             |    |

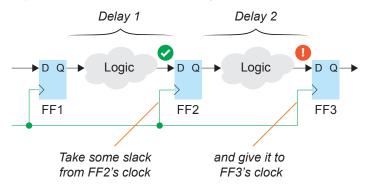

|       | Beneficial Skew                                     |    |

|       | Sweeping Script                                     |    |

|       | Optimization Sweeping                               |    |

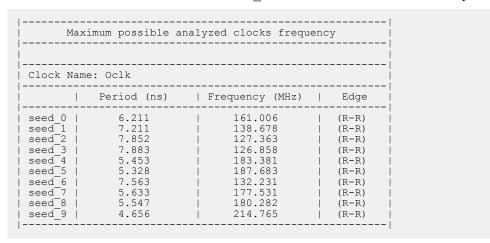

|       | Seed Sweeping                                       |    |

|       | Closing Timing with High DSP Block Utilization      |    |

|       |                                                     |    |

| ici T | iming Report and Flow Commands                      |    |

|       | Timing Commands                                     | ბნ |

| Revision History                                  | 95 |

|---------------------------------------------------|----|

| Where to Learn More                               | 94 |

| About the < <i>project</i> >.pt_timing.rpt File   |    |

| About the <i><project></project></i> .pt.sdc File |    |

| Appendix                                          | 90 |

| report_timing_summary Command                     |    |

| report_timing Command                             | 88 |

| report_clocks Commandreport_path Command          |    |

| report_clocks Command                             |    |

# Introduction

Closing timing is an important part of the design process. The Efinity® software includes tools and reports to help you understand your design's timing requirements and let you adjust settings to close timing. This document explains how to set timing constraints using a Synopsys Design Constraints (.sdc) file, and discusses synthesis, placement, and routing options to customize the Efinity® flow.

You can explore timing with just an RTL design and an SDC file. This step helps you understand your design's timing requirements in general terms. If you have not built an interface yet, the placer auto-assigns the interface signals, which you can use to set constraints. After you build your interface, the interface signals are constrained according to the assignments you made in the Interface Designer.

**Note:** This document includes information that was previously provided in AN 008: Setting Trion Timing Constraints in the Efinity Software.

# **About Constraints**

The Efinity® software supports the Synopsys Design Constraints format for specifying timing constraints. The software validates the timing performance of your design's core logic using industry-standard constraint, analysis, and reporting methodology. During compilation, the software generates a timing analysis report. The pins, nets, and ports used with SDC constraints refer to the post-synthesis netlist.

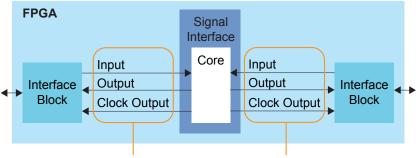

Trion® and Titanium FPGAs feature interface blocks—I/O logic and buffers, I/O banks, PLLs, etc.—that connect the core logic to the package pins. You use the Efinity® Interface Designer to configure these interface blocks for your design. After you configure these blocks, you generate a constraint template file (project>.pt.sdc) that you use as the basis for your design's SDC file. You can also refer to report files for the interface blocks, which you can view in the Results tab under the Efinity® Dashboard.

- For synchronous (registered) interfaces, the template defines clocks and sets input and output delays for your design. You simply copy and paste the relevant lines from the SDC template file to your own SDC file and adjust the timing as needed.

- For non-synchronous (unregistered) interfaces, you need to determine the interface timing and board timing and add those to your core settings.

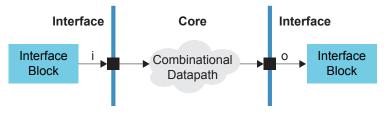

**Important:** Unlike traditional FPGAs, with Trion<sup>®</sup> and Titanium FPGAs you make timing constraints at the core level, not the interface or package level.

Efinix recommends that you use registered interfaces as much as possible to simplify the SDC you need.

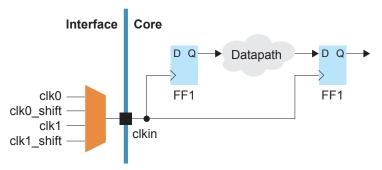

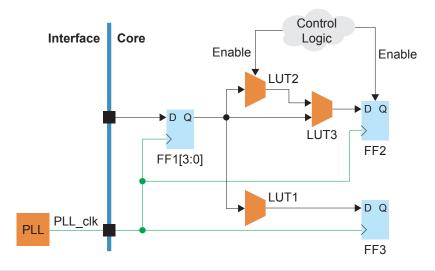

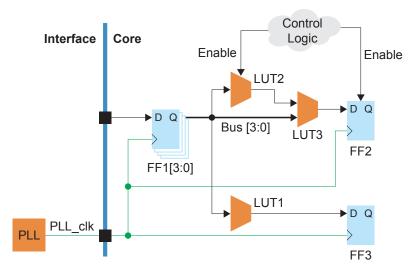

Figure 1: Set Constraints at the Core Level

Constrain signals to/from interface and core

**Note:** Refer to SDC Constraints (Alphabetical) on page 52 for a list of supported SDC constraints and object specifiers.

# Tools for Exploring Timing

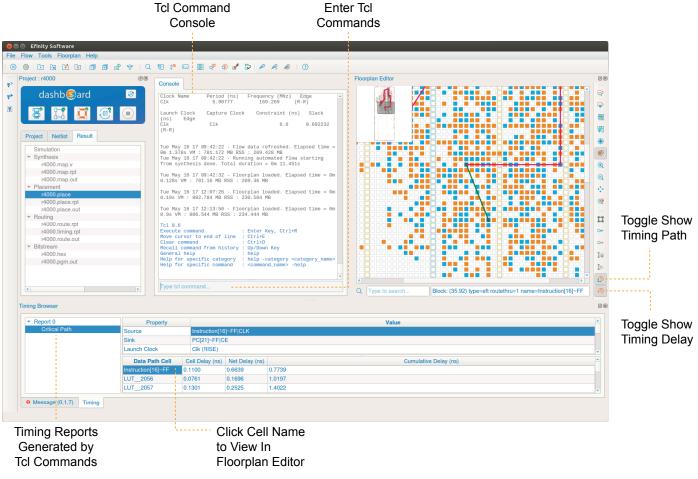

You use static timing analysis (STA) to measure the timing performance of your design. The software generates a timing report based on the design's place and route results and the project's SDC file. The software provides several tools for viewing and cross-probing timing results:

- The Timing Browser helps you explore your design's critical paths and the cells of those paths.

- The Floorplan tool shows the locations of the paths and cells in the fabric.

- The Tcl Command Console helps you analyze and explore timing.

To explore timing, open the Tcl Command Console, the Timing Browser, and the Floorplan Editor. In the Tcl Command Console, enter commands to query timing reports. The software reports specific timing paths based on their slack or propagation delay. For example:

- Use the report\_path command to query propagation delays between the specified end points.

- Use the report timing command to query the slack between the specified end points.

Specify the details of the timing path that you want to analyze. You can specify the starting and ending points explicitly or leave them as implicit. The software analyzes the timing path based on the arguments provided to the constraints.

The software displays Tcl reports in the Timing Browser.

- Click on the report name to view details.

- Click on cell names under **Data Path Cell** to view the location of the cell in the Floorplan Editor.

- Turn on Show Timing Path or Show Timing Delay in the Floorplan Editor to see the path and delay for a particular cell.

**Note:** The place-and-route data for your project has to be loaded for you to use the Timing Browser and Floorplan tool. Refer to "Auto-Load Place-and-Route Data" in the **Efinity Software User Guide** for instructions on loading it.

Figure 2: Using the Timing Browser

(i)

**Note:** Refer to Tcl Timing Report and Flow Commands on page 86 for more information on available commands. For help on available Tcl commands, type help -category <sdc or timing> in the Tcl Command Console.

# **SDC File Overview**

Generally, the steps you follow when creating a new SDC file are:

- 1. Create an empty SDC file.

- 2. Add the file to your project. (You can also add multiple files.)

- 3. Have the ct>.pt.sdc and ct>.pt\_timing.rpt files ready so you can use them when creating constraints.

- 4. Identify clocks and their relationships.

- 5. Identify I/O constraints.

- 6. Identify any timing exceptions.

- 7. Debug your SDC constraints.

The following sections go over these steps in detail with examples.

# **About SDC Files**

An SDC file is simply a text file with one constraint per line; however, you need to keep some rules in mind when creating it:

- The order of the constraints in the SDC file is important. If there are dependencies between any of the constraints, you must ensure that you have written them in the correct order for them to be valid.

- If a constraint has incorrect syntax, the software ignores it and issues a warning message.

- For some constraints, the argument order is important for the constraint to be valid.

- The minimum content required in an SDC file is a create\_clock constraint. You should *always* set a clock constraint—even if it is a virtual clock—whenever you create an SDC file.

**Important:** SDC is case sensitive. If you are using VHDL, which is not case sensitive, be careful when declaring net names. The Efinity software converts all names to lowercase letters during synthesis. Therefore, the SDC should use lowercase letters not mixed case or uppercase.

If you do not define an SDC file, the software defaults to creating clocks with a period of 1 ns for every clock source in your design and does not constrain any I/O pins. It assumes that all of the clocks it finds are related. The Efinity® timing analyzer then identifies the critical path based on this default constraint.

### Constraint Order

First, define the clocks and other timing assertions in this order:

- 1. Primary clocks

- 2. Virtual clocks

- 3. Generated clocks

- 4. Clock groups

- 5. Input and output delays

Then, define any timing exceptions, in this order:

- 1. False paths

- 2. Maximum and minimum delays

- 3. Multicycle paths

# Create an Empty SDC File

You can use the Efinity<sup>®</sup> Code Editor or any text editor to create an SDC file and save it into your project directory.

If you are working with a new project, start by creating an empty SDC file. Then, copy and paste the Interface Designer-generated SDC constraints into this empty file and modify them to meet your timing requirements.

If you are porting an existing design to Efinix FPGAs, you may already have an SDC file. You may still want to start with an empty SDC file, copy the Interface Designer-generated constraints to the new file and modify them as needed, and then add in any additional constraints from your existing SDC file.

# Add an SDC File to Your Project

Add one or more SDC files to your project using these steps:

- 1. Choose File > Edit Project.

- 2. Click the Design tab.

- 3. Click the Add SDC file button next to the SDC box.

- **4.** Browse to the file you created and click **Open**.

- 5. Click OK.

If you add multiple SDC files, the software processes them in the order shown in the table.

**Tip:** As a shortcut, in the Project pane you can right-click **<project name> > Constraint** to pop-up a context-sensitive menu. Choose **Add** if you already have an SDC file or **Create** if you want to create a new empty file.

# Using Multiple SDC Files

The Efinity software v2023.1 and higher allows you to use multiple SDC files in your project. You add additional SDC files in the Project Editor. SDC files are processed in the order listed.

During compilation, the software reads the SDC files in order starting from the first listed file and continuing to the next one(s). The same constraint order rules apply to the SDC file list. The software displays messages about the SDC file(s) in the Console. The software reads the files at the beginning of the routing stage. If the software detects any errors in the SDC file(s), it shows the error, file name, and line number.

# Efinity Files You Use to Create Constraints

When you generate constraints in the Interface Designer or compile your project, the Interface Designer generates the project>.pt.sdc and project>.pt\_timing.rpt files in the outflow directory. You use these files as a reference when you create your SDC file.

- project > .pt.sdc has timing constraints for the design's interface that you build with the Interface Designer.

This following sections explain how to use these files to create your SDC.

For more information on these files, refer to:

- < project > .pt.sdc

- < project > .pt\_timing.rpt

For more information on using the Interface Designer, refer to:

- Titanium Interfaces User Guide

- Trion® Interfaces User Guide

# Constraining Clocks

The first task when building an SDC file is to define your design's clocks and their relationships. You set constraints to define the clocks and any relationships they have to each other. Then, you can constrain the I/O pins relative to each clock as needed. The following sections explain the theory behind defining clocks and their relationships.

**Learn more:** The following application notes provide information on clock and reset guidelines:

AN 040: Clocking Source-Synchronous Designs

AN 042: Working with PLLs

AN 044: Aligning LVDS Clock and Data

AN 046: Reset Guidelines for Efinix FPGAs

# **Defining Clocks**

Clock sources can come from interface blocks like PLLs or oscillators, or they can come from your board to the core through GPIO pins. You define and identify clocks using the create clock and create generated clock constraints.

The create\_clock constraint defines a real or virtual clock with a specific duty cycle and period (ns). Each target can have multiple clocks associated with it.

### **Example: Define a Clock**

This constraint creates a clock, clk1, with a period of 10 ns:

```

create clock -period 10 -name clk1 [get ports clk1]

```

**Tip:** As you may remember from physics class, the clock period is the inverse of the frequency (T = 1/f). So if you want to specify the period in ns for a 50 MHz clock frequency, you use this calculation:

T = (1/50 MHz) \* 1000 Hz/MHz = 20 ns

The -waveform option lets you define the clock's rising and falling edges.

### **Example: Define a Clock with a Waveform**

This example defines a clock with a 10 ns period and 50/50 duty cycle, but the first rising clock edge is phase shifted 25% to start at 2.5 ns.

```

create clock -period 10.00 -waveform {2.50 7.50} -name clk1 [get ports clk1]

```

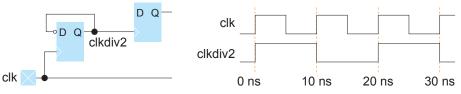

The create\_generated\_clock constraint defines a relationship between an internally generated clock and its source clock. This constraint only supports the divide\_by, multiply by, duty cycle, and invert options.

### **Example: Creating Clocks**

The following example shows the constraints for the base clock clk and the internally generated clock clkdiv2.

```

create_clock -name clk -period 10 [get_ports clk]

create_generated_clock -source clk -divide_by 2 clkdiv2

```

Virtual clocks are clocks that are not assigned to a timing node. They are used to represent off-chip clocks and are used in set input delay and set output delay constraints.

For more details, refer to:

- create\_clock Constraint on page 52

- create generated clock Constraint on page 53

## Using the create\_clock Constraint

Any interface block that can be a clock source (PLL, GPIOs, MIPI RX Lane, MIPI RX/TX PHY, and JTAG) has an auto-generated <code>create\_clock</code> constraint in the <code><project>.pt.sdc</code>. There are several cases:

- Constraints where the software knows the clock value. < project > .pt.sdc includes the number.

- Constraints where you have to define the clock value (typically, GPIO resources being

used as GCLK, RCLK, and JTAG TCK). These constraints are commented out and have

a placeholder for you to add in the number.

A GPIO with a connection type other than GCLK, RCLK, or JTAG TCK does not have a template (because the software thinks they are not clocks). You need to write your own create clock command.

Tip: Common mistakes when using create clock SDC command:

Using the *-name* option without a target (e.g., get\_ports) and thereby creating a virtual clock by mistake. The Efinity software prints an info message when it finds a virtual clock definition.

Using the instance name instead of the clock pin name. The clock pin name you use in the Interface Designer is the name used in the core timing netlist.

### Example: PLL

The PLL Timing Report section shows the details about the clock generated by PLLs in the interface. Details including clock period, phase shift, and whether the clock is inverted are listed in the section. You copy the constraints from project.pt.sdc into your SDC file, you do not need to change them.

```

# PLL Constraints

#########################

create_clock -period 10.0000 i_hbramClk_fb

create_clock -waveform {1.2500 3.7500} -period 5.0000 i_hbramClk90

...

```

### Example: GPIO Clock (GCLK and RCLK)

The following sections have create\_clock constraint templates that you need to modify:

- GPIO Constraints

- HSIO GPIO Constraints (Titanium only)

To constrain these clocks, replace <USER\_PERIOD> in the create\_clock template line with the clock period and uncomment the line. If necessary, you can define the waveform if the clock is not using a standard 50/50 duty cycle.

### **Example: Template**

### **Example: Your SDC File**

```

create clock -period 10 [get ports {clock}]

```

### Example: Regular GPIO Used as a Clock

You need to use a regular GPIO as a clock, for example if you need a bidirectional signal that sometimes acts as a clock. In this case you need to write your own create\_clock command because the software cannot generate a template for it.

For simple inputs and outputs, the instance name and pin name are usually the same (just to make things easier). A GPIO in input mode has three pins with different names. The following example has instance bolk with 3 pin names for the input, output, and output enable.

### **Example: Timing Report for GPIO in inout Mode**

For this case, the create\_clock constraint is:

```

create_clock -period 10 -name bclk [get_ports bclk_IN]

```

**Note:** The constraint does not use bclk for get\_ports, it uses the pin name not the instance.

# Using the create\_generated\_clock Constraint

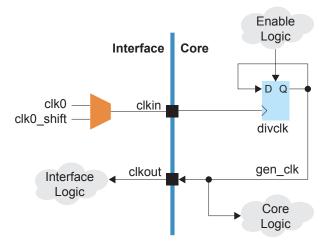

The Interface Designer does not create SDC constraints for generated clocks. Typically, you implement the generated clock in the core design by dividing down interface clocks. You need to add constraints for these clocks.

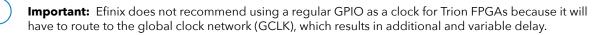

Figure 3: Divide Down Clock

### **SDC Commands:**

create\_clock -period 10 -name clk0 [get\_ports clkin]

create\_generated\_clock -source [get\_ports clkin] -divide\_by 2 [ get\_pins divclk|Q ] -name

gen\_clk0

### Virtual Clocks

A virtual clock represents a system clock that is on the board but is off-chip from the FPGA. In your SDC files, you should use a virtual clock as a reference clock for the input and output delay instead of the board clock. The virtual clock provides a clean interface clock and means you do not have to worry about the shifted waveform on the board. Additionally, the virtual clock prevents timing analysis from treating the I/O path with overly tight and unrealistic requirements.

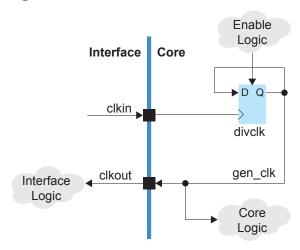

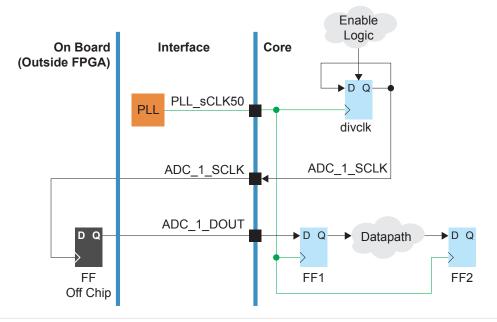

The following figure shows a virtual clock used with the set\_input\_delay command. The oscillator drives the clock pad, clk\_in, and the clock pin of an external off-chip flipflop. The path from the oscillator to the clk\_in pad on the core is through the interface. The Interface Designer can add extra clock latency and clock uncertainty to that path. To

remove any extra clock latency and uncertainty for the data\_in pad, you use a virtual clock.

Figure 4: Virtual Clock with set\_input\_delay Example

### **Example: SDC Commands**

```

create_clock -period 40 -name clk_in [get_ports clk_in]

create_clock -period 40 -name virtual_clk

set_input_delay -clock virtual_clk -max 0.3 [get_ports data_in]

set_input_delay -clock virtual_clk -min 0.1 [get_ports data_in]

```

Notice that virtual clock has the same period and characteristics as clkin but it does not have a clock target referring to a net, port, or pin in the netlist. The Efinity software displays an info message for the virtual clock.

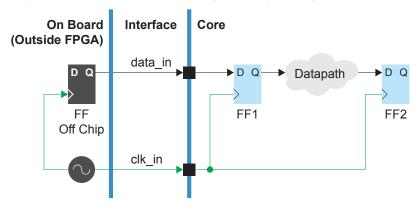

The following figure shows how to use a virtual clock with the set\_output\_delay command.

Figure 5: Virtual Clock with set\_output\_delay Example

### **Example: SDC Commands**

```

create_clock -period 40 -name clk in [get_ports clk_in]

create_clock -period 40 -name virtual_clk

set_output_delay -clock virtual_clk -max 0.4 [get_ports data_out]

set_output_delay -clock virtual_clk -min 0.3 [get_ports data_out]

```

**Note:** In your SDC file, put the virtual clock and core clock in the same clock group so they are related. The software can then analyze the transfers from virtual\_clk to/from clk\_in. See Clock Relationships on page 26.

# **Clock Latency**

The source clock latency represents the time it takes to get from the clock source on the board to the global clock tree on the FPGA. This delay includes the board delay, buffer delay, and any PLL delay (including PLL compensation delay, which is negative, see AN 042: Working with PLLs).

Most of the time you do not need to use set\_clock\_latency. However, it is required when you want to constrain external signals to core registers to capture the latency effect of the clock signal transferring onto the FPGA.

You need to calculate the delay based on the GPIO mode, PLL mode, and any board delays.

The Efinity software v2023.2 and higher creates a template for the set\_clock\_latency constraint in the project.pt.sdc file. The following topics explain how to calculate clock latency for GPIO and PLL clocks and how to use the template to create the SDC constraints.

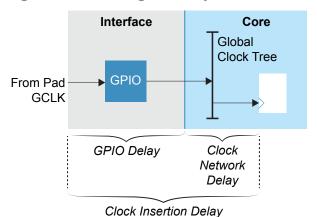

# **GPIO Clock Latency**

When using a GPIO as a clock source you need to account for the any board delay and the GPIO input buffer delay.

Figure 6: GBUF to Register Delay

The SDC constraint formulas for the receive clock delay are:

```

set_clock_latency -source -setup <max calculation> <clock ports>

set_clock_latency -source -hold <min calculation> <clock ports>

```

### The equations are:

<max calculation> = <max board constraint> + GPIO CLK IN<sub>max</sub>

<min calculation> = <min board constraint> + GPIO CLK IN<sub>min</sub>

The following example shows how to calculate the delays and set the constraints.

### **Example: Setting GPIO Clock Latency**

You need to define the clock latency before the core clock pin clk. This example assumes that the clock and data traces on the board are well matched; therefore, there is no external board delay.

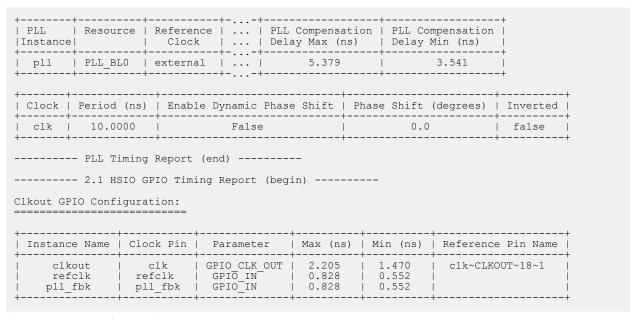

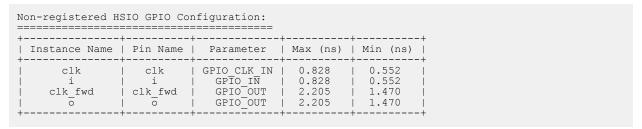

The GPIO clock buffer delays are shown in the Excerpt of project>.pt\_timing.rpt: (non-registered GPIO table):

The ct>.pt.sdc template is:

There is no board delay in this example, therefore, the equations are:

```

< max\ calculation > = 0 + 0.828 = 0.828

```

$< min \ calculation > = 0 + 0.552 = 0.552$

The resulting constraints are:

```

set_clock_latency -source -setup 0.828 [get_ports clk]

set_clock_latency -source -hold 0.552 [get_ports clk]

```

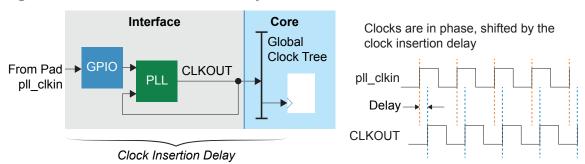

# PLL Local Feedback Clock Latency

When using a PLL as a clock source you need to account for the any board delay, the GPIO input buffer delay (for the PLL's reference clock pin), and the PLL compensation delay.

When the PLL is in local feedback mode, the compensation delay is zero.

Figure 7: PLL Local Feedback Mode Delay

The SDC constraint formulas for the receive clock delay are:

```

set_clock_latency -source -setup <max calculation> <clock ports>

set_clock_latency -source -hold <min calculation> <clock ports>

```

### The equations are:

<max calculation> = <max board constraint> + GPIO\_IN<sub>max</sub> - <PLL compensation> <min calculation> = <min board constraint> + GPIO\_IN<sub>min</sub> - <PLL compensation>

The Efinity software v2023.2 and higher calculates the GPIO input buffer and PLL compensation delays and provides them in a template in the *project>.pt.sdc file. You still need to add any board delays if needed.*

The following example shows how to calculate the delays and set the constraints.

### **Example: Setting PLL Local Feedback Clock Latency**

In this example, the PLL clock output is called clk. This example assumes that the clock and data traces on the board are well matched; therefore, there is no external board delay.

For the GPIO\_IN delays, this example uses the values for the i pin.

The PLL compensation delay is 0 in this mode.

Excerpt of ct>.pt\_timing.rpt:

The ct>.pt.sdc template is:

There is no board delay in this example, therefore, the equations are:

```

< max\ calculation > = 0 + 0.828 = 0.828

```

$< min\ calculation > = 0 + 0.552 = 0.552$

The resulting constraints are:

```

set_clock_latency -source -setup 0.828 [get_ports clk]

set_clock_latency -source -hold 0.552 [get_ports clk]

```

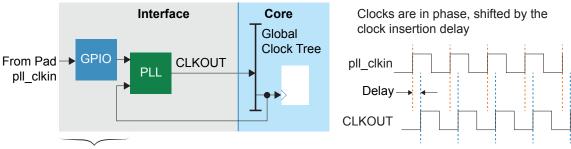

# PLL Core Feedback Clock Latency

When using a PLL as a clock source you need to account for the any board delay, the GPIO input buffer delay (for the PLL's reference clock pin), and the PLL compensation delay.

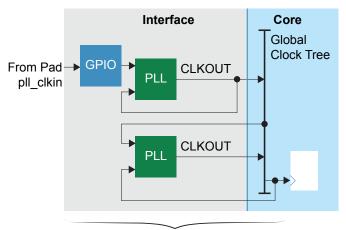

Figure 8: Core Feedback Mode Delay

Clock Insertion Delay

When the PLL is in core feedback mode, the compensation delay is equal to the clock network delay.

The SDC constraint formulas for the receive clock delay are:

```

set_clock_latency -source -setup <max calculation> <clock ports>

set_clock_latency -source -hold <min calculation> <clock ports>

```

### The equations are:

<max calculation> = <max board constraint> + GPIO\_IN<sub>max</sub> - <PLL compensation>

<min calculation> = <min board constraint> + GPIO\_IN<sub>min</sub> - <PLL compensation>

The Efinity software v2023.2 and higher calculates the GPIO input buffer and PLL compensation delays and provides them in a template in the *project>.pt.sdc file. You still need to add any board delays if needed.*

### **Example: Setting PLL Core Feedback Clock Latency**

In this example, the PLL clock output is called clk. This example assumes that the clock and data traces on the board are well matched; therefore, there is no external board delay.

Excerpt of ct>.pt\_timing.rpt:

The ct>.pt.sdc template is:

### The equations are:

```

<max calculation> = 0 - 2.834 = -2.834

<min calculation> = 0 - 1.457 = -1.457

```

The numbers are negative because the PLL compensation is so much larger than the input delay.

The resulting constraints are:

```

set_clock_latency -source -setup -2.834 [get_ports clk]

set_clock_latency -source -hold -1.457 [get_ports clk]

```

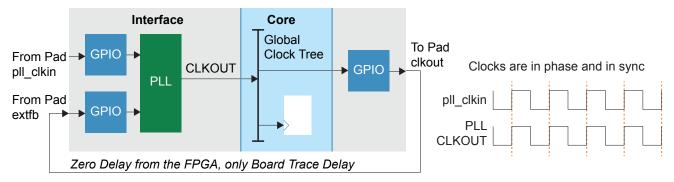

# PLL External Feedback Clock Latency

When using a PLL as a clock source you need to account for the any board delay, the GPIO input buffer delay (for the PLL's reference clock pin), and the PLL compensation delay.

**Note:** Trion FPGAs do not have external feeddback mode.

Figure 9: External Feedback Mode Delay

When the PLL is in external feedback mode, the compensation delay is equal to GPIO\_IN plus the clock network delay plus GPIO\_CLK\_OUT.

The SDC constraint formulas for the receive clock delay are:

```

set_clock_latency -source -setup <max calculation> <clock ports>

set_clock_latency -source -hold <min calculation> <clock ports>

```

### The equations are:

<max calculation> = <max board constraint> + GPIO\_IN<sub>max</sub> - <PLL compensation>

<min calculation> = <min board constraint> + GPIO\_IN<sub>min</sub> - <PLL compensation>

The Efinity software v2023.2 and higher calculates the GPIO input buffer and PLL compensation delays and provides them in a template in the *project>.pt.sdc file. You still need to add any board delays if needed.*

The following example shows how to calculate the delays and set the constraints.

### **Example: Setting PLL External Feedback Clock Latency**

In this example, the PLL clock output is called clk. This example assumes that the clock and data traces on the board are well matched; therefore, there is no external board delay.

Excerpt of ct>.pt\_timing.rpt:

The ct>.pt.sdc template is:

The equations are:

```

<max calculation> = 0 - 4.551 = -4.551

<min calculation> = 0 - 2.989 = -2.989

```

The numbers are negative because the PLL compensation is so much larger than the input delay.

The resulting constraints are:

```

set_clock_latency -source -setup -4.551 [get_ports clk]

set_clock_latency -source -hold -2.989 [get_ports clk]

```

# PLL Cascading Clock Latency

When using cascaded PLLs as a clock source you need to account for the any board delay, the GPIO input buffer delay (for the PLL's reference clock pin), and the PLL compensation delay.

**Note:** You should cascade a maximum of 1 PLL, that is, the source PLL and the cascaded one.

Figure 10: PLL Cascade Delay

Clock Insertion Delay

The SDC constraint formulas for the receive clock delay are:

```

set_clock_latency -source -setup <max calculation> <clock ports>

set_clock_latency -source -hold <min calculation> <clock ports>

```

The equations for the source PLL are:

<max calculation> = <max board constraint> - <source PLL clock latency>

<min calculation> = <min board constraint> - <source PLL clock latency>

The equations for the cascaded PLL are:

<max calculation> = <source PLL clock latency>max + <cascaded PLL clock latency>max

$< min\ calculation > = < source\ PLL\ clock\ latency > min\ + < cascaded\ PLL\ clock\ latency > min$

The Efinity software v2023.2 and higher calculates the GPIO input buffer and PLL compensation delays and provides them in a template in the *project>.pt.sdc* file. You still need to add any board delays (if needed).

For the cascaded PLL, the software includes the clock network delay in the PLL compensation delay value.

The following example shows how to calculate the delays and set the constraints.

### **Example: PLL Cascading Clock Latency**

In this example, the PLL clock output is called clk. This example assumes that the clock and data traces on the board are well matched; therefore, there is no external board delay.

Excerpt of ct>.pt\_timing.rpt:

```

----- 1. PLL Timing Report (begin) ------

+-----

| PLL Instance | Resource | Reference Clock | ... | PLL Compensation Delay Max (ns) | PLL

Compensation Delay Min (ns) |

-----

| src pll | PLL_BLO | external | ... | 1.519

2.346

| casc_pll | PLL_BL1 | core | ... |

| 1.516 | |

2.341

| Clock | Period (ns) | Enable Dynamic Phase Shift | Phase Shift (degrees) | Inverted |

| 0.0 | false

| 0.0 | false

----- PLL Timing Report (end) -----

----- 2. GPIO Timing Report (begin) ------

Non-registered GPIO Configuration:

| Instance Name | Pin Name | Parameter | Max (ns) | Min (ns) |

refclk | refclk | GPIO_IN | 0.828 | 0.552 |

```

The ct>.pt.sdc template is:

The equations for the source PLL are:

```

< max\ calculation > = 0 - 1.517 = -1.517

```

$< min\ calculation > = 0 - 0.967 = -0.967$

The equations for the cascaded PLL are:

$< max\ calculation > = 0 - 1.517 + 0.004 = -1.513$

$< min\ calculation > = 0 - 0.967 + 0.003 = -0.964$

The numbers are negative because the PLL compensation is so much larger than the input delay.

The resulting constraints are:

```

set_clock_latency -source -setup - 1.517 [get_ports {src_pll_clk}]

set_clock_latency -source -hold - 0.967 [get_ports {src_pll_clk}]

set_clock_latency -source -setup - 1.513 [get_ports {casc_pll_clk}]

set_clock_latency -source -hold - 0.964 [get_ports {casc_pll_clk}]

```

# **Clock Relationships**

By default, the Efinity® software assumes that all clocks are related and it analyzes the timing between all clock domains and optimizes all possible paths.

If you set constraints for two clocks, and do not cut the path between them, the software tries to find the tightest clock-to-clock delay requirement between them. If the timer cannot find a common clock period for the two clocks after 1,000 clock cycles, it determines that they are *non-expandable*. The timer gives these clocks a default constraint of 0.01 ns. If you want to override this default, use the set max delay or set min delay constraint.

**Important:** Efinix recommends that you explicitly set constraints to indicate unrelated clocks. That way the software does not perform unnecessary path optimization, which can lead to problems with closing timing.

# Setting Constraints for Unrelated Clocks

The first step is to analyze your design to determine which clocks are related and which are not. You then use one of the following constraints:

- set\_clock\_groups—Use when you want to specify bidirectional constraints between clocks. Generally, this is the simplest method, and the fastest for the Efinity® timer to analyze. (See set clock groups Constraint on page 54.)

- set\_false\_path—Use when you want to be specific about which clocks connect with which end points. This constraint is one-directional, so you need to specify two constraints, one for each direction. (See set\_false\_path Constraint on page 55.) Typically, you use these constraints when you want to indicate timing exceptions for a subset of timing end points in one of the clock domains.

# Using the set\_clock\_groups Constraint

Use this constraint to define the relationship between the clocks and generated clocks you defined. Typically, only clocks from the same source are related to each other. For example, clock outputs from the same PLL or clocks from a single clock pin. Any other clocks should be specified as unrelated.

Unrelated clock groups can be exclusive or asynchronous.

- Exclusive clock groups do not operate at the same time as each other.

- Asynchronous clock groups have no timing relationship between them, for example, clocks driven from two independent PLLs.

You use the <code>-exclusive</code> or <code>-asynchronous</code> options to define how to treat the clock groups. The Efinity® software treats both options identically, but some third-party EDA tools use these constraints when checking for proper clock domain crossing logic. Therefore, it is a good idea to use the correct option for the relationship.

To illustrate how to set constraints using set\_clock\_groups, consider a design with four clocks, clk1, clk2, clk3, and clk4. After design analysis, you determine that clk1 and clk2 are related to each other and clk3 and clk4 are unrelated to all others. There are two ways to use the set\_clock\_groups constraint, both of which are correct.

### **Example: Use a Single Constraint**

The first method is to define the clocks and groups with a single constraint:

set\_clock\_groups -exclusive -group {clk1 clk2} -group {clk3} -group {clk4}

This constraint defines the relationship between clocks clk1, clk2, clk3, and clk4. If you later add an additional clock, clk5, and do not update the constraints, the software assumes that clk5 is synchronous to all other clocks.

### **Example: Use Separate Constraints**

The second method is to use separate constraints for each group:

```

set_clock_groups -exclusive -group {clk1 clk2}

set_clock_groups -exclusive -group {clk3}

set_clock_groups -exclusive -group {clk4}

```

In this case, each set\_clock\_groups constraint only specifies one group, which tells the software that the clocks in a given group are asynchronous to all others. With this method, if you later add clk5, the software would consider it to be asynchronous to clk1, clk2, clk3, and clk4.

It can be tempting to use the second method in case you forget a clock or add one later. However, whichever method you choose, Efinix recommends that you *always include constraints for each clock* in your design and that you update your SDC file when you add clocks.

# Using the set\_false\_path Constraint

The set\_false\_path constraint lets you be more specific when setting clock constraints. This constraint lets you cut the connection between a starting point (from) and an ending point (to). The from and to can be registers, I/O, or clocks.

The following constraint cuts the connection from clk1 to clk2:

```

set_false_path -from clk1 -to clk2

```

Remember, though, that this only cuts the connection in one direction. To specify that there is no relationship between clk1 and clk2, you also need to use the following constraint:

```

set_false_path -from clk2 -to clk1

```

### **Example: Using set\_false\_path Constraints**

A complete example of the constraints needed for our hypothetical four-clock design is:

```

set_false_path -from clk1 -to clk3

set_false_path -from clk1 -to clk4

set_false_path -from clk2 -to clk3

set_false_path -from clk2 -to clk4

set_false_path -from clk3 -to clk1

set_false_path -from clk3 -to clk2

set_false_path -from clk3 -to clk2

set_false_path -from clk3 -to clk4

set_false_path -from clk4 -to clk4

set_false_path -from clk4 -to clk1

set_false_path -from clk4 -to clk2

set_false_path -from clk4 -to clk2

set_false_path -from clk4 -to clk3

```

When you want to cut paths between clock domains, as in this simple example, Efinix recommends that you use set\_clock\_groups instead of set\_false\_path. The set\_false\_path constraint becomes more useful when you want to specify exceptions for registers or I/O, or if you want to cut only one direction of a clock domain pair.

### **Example: Cut Path to a Port or Pin**

To cut only the path from clk1 to a port named testout:

```

set_false_path -from clk1 -to [get_ports testout]

```

To cut only the path from clk1 to a pin named testout:

```

set false path -from clk1 -to [get pins instance|testout]

```

# Clock Synchronizers

If you have asynchronous clock groups and want to transfer data between them, you need to add synchronizing registers (also known as synchronizers). Synchronizers are register chains in the receiving clock domain that capture data from the sending domain. They prevent metastable events from propagating into the receiving clock domain.

To designate a register as a synchronizer, use the async reg synthesis attribute.

When async\_reg is true, synthesis does not perform optimization to reduce, merge, or duplicate these registers. During place and route, the software keeps these registers close together to improve synchronization between asynchronous clock domains.

Verilog HDL:

```

(* async_reg = "true" *) reg [1:0] x;

```

### VHDL:

```

attribute async_reg: boolean; attribute async_reg of x : signal is true;

```

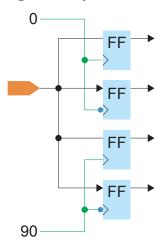

# Metastable Synchronizer Circuit

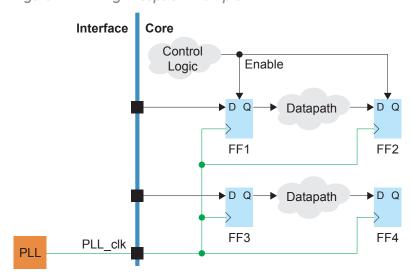

This example shows a synchronizer, which is a circuit that stabilizes an input signal that may produce a metastable output. If possible, the registers in a synchronization chain need to be placed close to each other. Efinix recommends that you use the async\_reg synthesis attribute for synchronizer registers.

In the following figure, FF1 and FF2 should be close together. Use the async\_reg synthesis attribute for the FF1 and FF2 registers in the RTL netlist., which tells the software to keep those registers close together during place-and-route.

max\_delay = 2 \* (fastest clock's period)

Max\_delay

Valid Shot

Data

Result Clock

Figure 11: Metastability Synchronizer Example

# How to Set Clock Uncertainty

Trion® and Titanium FPGAs have a default clock uncertainty for setup and hold analysis. You can view the clock uncertainty in the Static Timing Analysis Report (< project name > .timing.rpt). If the you have not set the uncertainty, the report uses the default value. For example, the T8 has 140 ps for setup and 50 ps for hold. You can modify these defaults by including the set\_clock\_uncertainty command in your SDC file.

One reason to add uncertainty is to account for the quality of the clock that feeds into the FPGA, or because you want the design to have more margin. However, keep in mind that clock uncertainty comes from the timing slack reported for your design, so increasing the uncertainty makes it harder to meet timing.

### **Example: Add 60 ps Clock Uncertainty**

You want to add 60 ps to the default uncertainty for clk for a T8 design. Add this command to your SDC file:

```

set clock uncertainty -to clk -setup 0.06

```

The Efinity® software uses 200 ps of clock uncertainty for setup analysis.

See set clock uncertainty Constraint on page 55 for details.

# Constraining I/O

As discussed earlier, you need to constrain the connections from the interface to the core. All connections between the core and interface are considered to be I/O for timing analysis.

If a given interface block is synchronizing the connection to the core, the Interface Designer SDC template includes the set\_input\_delay and set\_output\_delay SDC constraints that you need to use. When it is not synchronized, you need to add external board delays to the values the Interface Designer shows.

**Note:** For Trion<sup>®</sup> and Titanium FPGAs, most interface connections are synchronous. The exceptions are GPIO blocks in bypass mode and LVDS blocks in x1 bypass mode.

Constrain I/O pins to be timing-equivalent to a register that is clocked with the real or virtual clock you defined. Then, use the set input delay and set output delay constraints.

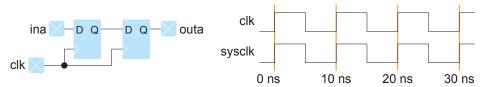

### **Example: Constraining I/O Pins**

In this example, sysclk is a virtual clock.

Figure 12: Clock and I/O Pin Constraint Example

Use these constaints to define the clock and set the delays for the pins:

```

create_clock -name clk -period 10 [get_ports clk]

create_clock -name sysclk -period 10

set_input_delay -clock sysclk -max 2.4 [get_ports ina]

set_output_delay -clock sysclk -max 1.2 [get_ports outa]

```

# Constraining Synchronous Inputs and Outputs

Synchronous inputs and outputs are interface signals that are connected to synchronous elements in the FPGA's periphery. Because the Interface Designer knows how the clock and data signals are connected to the synchronous elements, the software can automatically determine the precise delays for the set\_input\_delay and set\_output\_delay constraints. These delays are provided in the project name.pt.sdc file. When the Efinity software generates the constraints for synchronized output and input pins, it creates a set\_output\_delay or set\_input\_delay that captures the delay values of the synchronous element and the core clock delay of the FPGA.

When the Efinity software models the timing, the minimum and maximum refer to different timing corners (fast corner and slow corner), not the minimum/maximum potential delay in one timing corner.

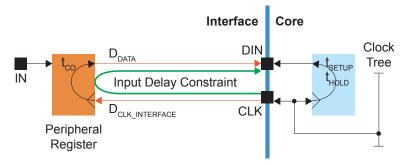

### **Understanding Input Delay Values**

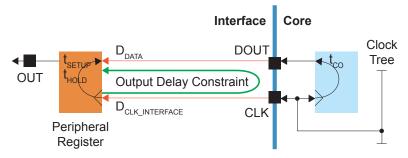

The following figure shows an example of a peripheral register, clock, clock-to-output delay, and data path.

Figure 13: Input Delay Example

- t<sub>CO</sub> is the peripheral register's clock-to-output delay.

- D<sub>DATA</sub> is the delay from the peripheral register to the core.

- $\bullet$   $\;D_{CLK\_INTERFACE}$  is the clock delay to the peripheral register.

So the equations for the output delay are:

Maximum input delay =  $D_{DATA}$  (max) +  $t_{CO}$  +  $D_{CLK}$  INTERFACE (max)

Minimum input delay = D<sub>DATA</sub> (min) + t<sub>CO</sub> + D<sub>CLK</sub> INTERFACE</sub> (min)

For example:

| Parameter                  | Max | Min |

|----------------------------|-----|-----|

| D <sub>DATA</sub>          | 2   | 1   |

| t <sub>CO</sub>            | 2   | 1   |

| D <sub>CLK_INTERFACE</sub> | 2   | 1   |

- Maximum input delay = 2 + 2 + 2 = 6

- Mininum input delay = 1 + 1 + 1 = 3

The generated constraint has the -reference\_pin option, which lets the software automatically calculate the core clock network delay.

### **Understanding Output Delay Values**

The following figure shows an example of a peripheral register, clock, setup/hold, and data path.

Figure 14: Output Delay Example

- t<sub>SETUP</sub> is the peripheral register's setup requirement.

- t<sub>HOLD</sub> is the peripheral register's hold requirement.

- D<sub>DATA</sub> is the delay from the core to the peripheral register.

- D<sub>CLK INTERFACE</sub> is the clock delay to the peripheral register.

So the equations for the output delay are:

Maximum output delay (setup) = D<sub>DATA</sub> (max) + t<sub>SETUP</sub> - D<sub>CLK</sub> INTERFACE</sub> (max)

Minimum output delay (hold) = D<sub>DATA</sub> (min) - t<sub>HOLD</sub> - D<sub>CLK INTERFACE</sub> (min)

For example:

| Parameter                  | Max | Min |

|----------------------------|-----|-----|

| D <sub>DATA</sub>          | 2   | 1   |

| t <sub>SETUP</sub>         | 2   | -   |

| t <sub>HOLD</sub>          | -   | 1   |

| D <sub>CLK_INTERFACE</sub> | 2   | 1   |

- Maximum output delay = 2 + 2 2 = 2

- Mininum output delay = 1 1 1 = -1

The generated constraint has the -reference\_pin option, which lets the software automatically calculate the core clock network delay.

### **Set Constraints**

To set a constraint for synchronous inputs and outputs in your constraints file:

- 1. Go to **Result** > **Interface** in the Efinity<sup>®</sup> dashboard.

- 2. Double-click < project name > .pt.sdc to open the report.

- 3. Copy the set\_input\_delay and set\_output\_delay constraints and paste them into your constraints file.

### **Example: set\_output\_delay Constraints**

```

set_output_delay -clock Clk -reference_pin [get_ports {Clk~CLKOUT~14~1}] -max 0.287

[get_ports {MemWrite}]

set_output_delay -clock Clk -reference_pin [get_ports {Clk~CLKOUT~14~1}] -min 0.161

[get_ports {MemWrite}]

```

# Constraining Unsynchronized Inputs and Outputs

Unsynchronized inputs and outputs are simple GPIO blocks in bypass mode or LVDS blocks in x1 bypass mode. For these blocks, you need to factor in any external board delays when calculating the -min and -max values for the input and output delays.

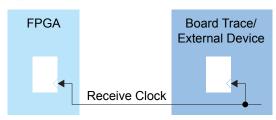

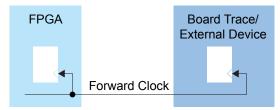

For blocks in bypass mode, the constraint clock is external to the FPGA:

- A receive clock is generated outside of the FPGA and is passed to the FPGA through a GPIO pin.

- A forward clock is generated by the FPGA and sent off chip though a GPIO pin in clock out mode.

Both receive and forward clocks synchronize the signal off chip.

For unsynchronized input or output signals, the GPIO block bypasses the register. GPIO\_IN represents a combinational delay from the pad through the I/O buffer. GPIO\_OUT represents a combinational delay to the pad through the I/O buffer from either the output or output enable signals.

The general procedure for constraining unsynchronized inputs and outputs is:

- 1. Determine which mode you are constraining (input receive, input forward, output receive, or output forward).

- 2. Find the minimum (fast) and maximum (slow) timing values in the Interface Designer report file < design name > .pt\_timing.rpt.

- 3. Use formulas (provided in later sections) to calculate the delay.

- 4. Add the constraint to your SDC file.

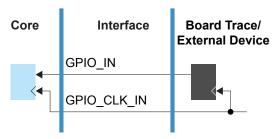

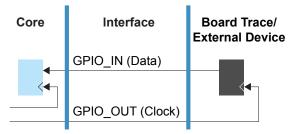

### Receive Clock

A receive clock is passed to the FPGA design by configuring a GPIO in input mode and and setting the connection type to GCLK or RCLK. GPIO\_IN\_CLK represents the combinational delay from the pad through the I/O buffer to the global clock tree.

Figure 15: Receive Clocks

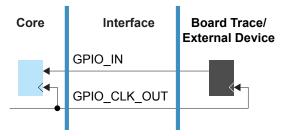

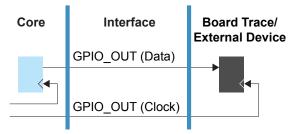

### Forward Clock Using GPIO in clkout Mode

A forward clock is generated by the FPGA design and sent off chip by configuring a GPIO in **clkout** mode. GPIO\_CLK\_OUT represents the combinational delay through the FPGA clock tree and the I/O buffer to the pad.

Figure 16: Forward Clocks

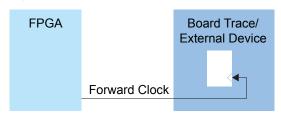

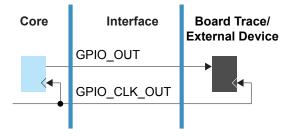

# Forward Clock Using GPIO in output Mode

Sometimes the clock generated by the FPGA is only used in the external system and is not a clock in the FPGA design. In this case, you use a regular GPIO block in **output** mode to forward the clock off chip.

Figure 17: Forward Clocks

# Input Receive Clock Delay

This example shows how to set constraints for an input receive clock.

Figure 18: Receive Clock Delay (GPIO Input, Register Bypass)

The SDC constraint formulas for the receive clock delay are:

```

set_input_delay -clock <clock> -max <max calculation> <ports>

set_input_delay -clock <clock> -min <min calculation> <ports>

```

### The equations are:

<max calculation> = <max board constraint> + GPIO\_IN<sub>max</sub>

<min calculation> = <min board constraint> + GPIO\_IN<sub>min</sub>

The following example shows how to calculate the delays and set the constraints.

### **Example: Constraining Input Receive Clock**

You want to constrain the din input with respect to clock clkin with a max board constraint of 4 ns and a min board constraint of 2 ns. The non-registered GPIO configuration data from the Interface Designer timing report file is:

| Non-registered GPIO Configuration: |                          |                                        |                             |                             |

|------------------------------------|--------------------------|----------------------------------------|-----------------------------|-----------------------------|

| +                                  | +                        | +                                      | +                           | +                           |

| Instance Name                      | Pin Name                 | Parameter                              | Max (ns)                    | Min (ns)                    |

| clkin<br>din<br>dout               | clkin<br>  din<br>  dout | GPIO_CLK_IN<br>  GPIO_IN<br>  GPIO_OUT | 1.954<br>  1.954<br>  4.246 | 0.526<br>  0.526<br>  1.081 |

The equations are:

$< max\ calculation > = 4 + 1.954 = 5.954$

$< min \ calculation > = 2 + 0.526 = 2.526$

The resulting constraints are:

```

set_input_delay -clock clkin -max 5.954 din

set_input_delay -clock clkin -min 2.526 din

```

**Note:** The GPIO\_CLK\_IN delay is accounted for in the set\_clock\_latency constraint. Therefore, you do not need to include it in the calculation for set input delay. Refer to Clock Latency on page 16.

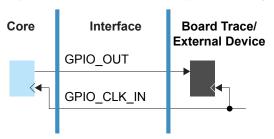

# Output Receive Clock Delay

This example shows how to set constraints for an output receive clock.

Figure 19: Receive Clock Delay (GPIO Output, Register Bypass)

The SDC constraint formulas for the receive clock delay are:

```

set_output_delay -clock <clock> -max <max calculation> <ports>

set_output_delay -clock <clock> -min <min calculation> <ports>

```

### The equations are:

<max calculation> = <max board constraint> + GPIO\_OUT<sub>max</sub>

<min calculation> = <min board constraint> + GPIO\_OUT<sub>min</sub>

The following example shows how to calculate the delays and set the constraints.

### **Example: Constraining Output Receive Clock**

You want to constrain the dout output with respect to clock clkin with a max board constraint of 4 ns and a min board constraint of 2 ns. The non-registered GPIO configuration data from the Interface Design report file is:

| on-registere         | ed GPIO Configu          | ration:<br>======                      |                             |                             |

|----------------------|--------------------------|----------------------------------------|-----------------------------|-----------------------------|

| Instance Na          | ame   Pin Name           | +<br>  Parameter                       | +<br>  Max (ns)             | +<br>  Min (ns)             |

| clkin<br>din<br>dout | clkin<br>  din<br>  dout | GPIO_CLK_IN<br>  GPIO_IN<br>  GPIO_OUT | 1.954<br>  1.954<br>  4.246 | 0.526<br>  0.526<br>  1.081 |

The equations are:

$< max \ calculation > = 4 + 4.246 = 8.246$

$< min\ calculation > = 2 + 1.081 = 3.081$

The resulting constraints are:

```

set_output_delay -clock clkin -max 8.246 dout

set_output_delay -clock clkin -min 3.081 dout

```

**Note:** The GPIO\_CLK\_IN delay is accounted for in the set\_clock\_latency constraint. Therefore, you do not need to include it in the calculation for set\_output\_delay. Refer to Clock Latency on page 16.

### Input Forward Clock Delay (GPIO clkout)

This example shows how to set constratints for an input forward clock.

**Warning:** Most designs do not need to use this method. For high-performance designs, you should use the GPIO registers and follow the instructions in **Constraining Synchronous Inputs and Outputs** on page 30.

Figure 20: Forward Clock Delay (GPIO Input, Register Bypass)

The SDC constraint formulas for the foward clock delay are:

```

set_input_delay -clock <clock> -reference_pin <clkout interface name> \

-max <max calculation> <ports>

set_input_delay -clock <clock> -reference_pin <clkout interface name> \

-min <min calculation> <ports>

```

#### Reference Pin

With forward clocks, you use the <code>-reference\_pin</code> option to include the clock latency delay in the I/O constraint. The <code>-reference\_pin</code> pin target is a clkout pad that the software automatically adds to the netlist. The <code><project>.pt\_timing.rpt</code> file shows the reference pin name.

Calculate the min and max constraints using the following equations:

<max calculation> = <max board constraint> + GPIO\_IN $_{max}$  + GPIO\_CLK\_OUT $_{max}$  <min calculation> = <min board constraint> + GPIO\_IN $_{min}$  + GPIO\_CLK\_OUT $_{min}$

The following example shows how to calculate the delays and set the constraints.

#### **Example: Constraining Input Forward Clock**

You want to constrain the i input with respect to clock clk\_fwd with a max board constraint of 2 ns and a min board constraint of 2 ns. The non-registered GPIO configuration data from the cproject.pt\_timing.rpt file is:

| Instance Name                                           | Clock Pin                | Parameter                              | Max (ns)      | Min (ns)                            | Reference Pin Name |

|---------------------------------------------------------|--------------------------|----------------------------------------|---------------|-------------------------------------|--------------------|

| clk_fwd                                                 | clk                      | GPIO_CLK_OUT                           | 2.205         | 1.470                               | clk~CLKOUT~219~1   |

| n-registered H                                          | SIO GPIO Con             | figuration:                            |               |                                     |                    |

| n-registered H.<br>==================================== | ++                       | ========<br>+                          | +<br>Max (ns) | +<br>Min (ns)                       |                    |

| Instance Name                                           | ++<br>  Pin Name  <br>++ | ====================================== | +             | +                                   |                    |

|                                                         | ++                       | +<br>Parameter  <br>+<br>GPIO_CLK_IN   | 0.828         | Min (ns)  <br>+<br>0.552  <br>0.552 |                    |

#### The equations are:

```

<max calculation> = 2 + 0.828 + 2.205 = 5.033 <min calculation> = 2 + 0.552 + 1.470 = 4.022

```

The resulting constraints are:

```

set_input_delay -clock clk -reference_pin clk~CLKOUT~219~1 -max 5.033 [get_ports {i}]

set_input_delay -clock clk -reference_pin clk~CLKOUT~219~1 -min 4.022 [get_ports {i}]

```

### Output Forward Clock Delay (GPIO clkout)

This example shows how to set constratints for an output forward clock.

**Warning:** Most designs do not need to use this method. For high-performance designs, use the GPIO registers and follow the instructions in **Constraining Synchronous Inputs and Outputs** on page 30.

Figure 21: Forward Clock Delay (GPIO Output, Register Bypass)

The SDC constraint formulas for the forward clock delay are:

```

set_output_delay -clock <clock> -reference_pin <clkout interface name> \

-max <max calculation> <ports>

set_output_delay -clock <clock> -reference_pin <clkout interface name> \

-min <min calculation> <ports>

```

Calculate the min and max constraints using the following equations:

```

<max calculation> = <max board constraint> + GPIO_OUT<sub>max</sub> - GPIO_CLK_OUT<sub>max</sub>

<min calculation> = <min board constraint> + GPIO_OUT<sub>min</sub> - GPIO_CLK_OUT<sub>min</sub>

```

The following example shows how to calculate the delays and set the constraints.

#### **Example: Constraining Output Forward Clock**

You want to constrain the o output with respect to clock clk\_fwd with a max board constraint of 2 ns and a min board constraint of 2 ns. The non-registered GPIO configuration data from the Interface Designer timing report file is:

The equations are:

```

< max\ calculation > = 2 + 2.205 - 2.205 = 2

```

$< min\ calculation > = 2 + 1.470 - 1.470 = 2$

The resulting constraints are:

```

set_output_delay -clock clk -reference_pin clk~CLKOUT~219~1 -max 2 [get_ports {o}]

set_output_delay -clock clk -reference_pin clk~CLKOUT~219~1 -min 2 [get_ports {o}]

```

### Input Forward Clock Delay (GPIO output)

This example shows how to set constratints for an input forward clock.

Figure 22: Forward Clock Delay (GPIO Input, Register Bypass)

The SDC constraint formulas for the foward clock delay are:

```

set_input_delay -clock <clock> -reference_pin <clkout interface name> \

-max <max calculation> <ports>

set_input_delay -clock <clock> -reference_pin <clkout interface name> \

-min <min calculation> <ports>

```

#### Reference Pin

With forward clocks, you use the <code>-reference\_pin</code> option to include the clock latency delay in the I/O constraint. The reference pin target is the pin name of the GPIO output used for the clock.

#### **Constraint Calculation**

Calculate the min and max constraints using the following equations:

```

<max calculation> = <max board constraint> + GPIO_IN<sub>max</sub>

+ < GPIO_OUT for clock pad><sub>max</sub>

<min calculation> = <min board constraint> + GPIO_IN<sub>min</sub>

+ < GPIO_OUT for clock pad><sub>min</sub>

```

The following example shows how to calculate the delays and set the constraints.

#### **Example: Constraining Input Forward Clock**

You want to constrain the i input with respect to clock clk\_fwd with a max board constraint of 2 ns and a min board constraint of 2 ns. The non-registered GPIO configuration data from the Interface Designer timing report file is:

| Non-re        | gistered HS             | SIO GPIO Com                   | nfiguration:                                         |                                        |                                        |

|---------------|-------------------------|--------------------------------|------------------------------------------------------|----------------------------------------|----------------------------------------|

| Inst          | ance Name               | Pin Name                       | Parameter                                            | +<br>  Max (ns)<br>+                   | +<br>  Min (ns)<br>+                   |

| <br> <br>  c. | clk<br>i<br>lk_fwd<br>o | clk<br>  i<br>  clk_fwd<br>  o | GPIO CLK_IN<br>  GPTO_IN<br>  GPIO_OUT<br>  GPIO_OUT | 0.828<br>  0.828<br>  2.205<br>  2.205 | 0.552<br>  0.552<br>  1.470<br>  1.470 |

For <GPIO\_OUT for clock pad>, use the GPIO OUT value for clk fwd.

The equations are:

```

< max\ calculation > = 2 + 0.828 + 2.205 = 5.033

```

$< min\ calculation > = 2 + 0.552 + 1.470 = 4.022$

The reference pin target is the forwarded clock, clk fwd.

In this example, the RTL is using a divided down clock, divclk, which is only used to drive the clk\_fwd signal off chip. Therefore, the set\_input\_delay constraint is relative to that generated clock. See Example: FPGA Forwarded Clock on page 60 for a more complete example.

The resulting constraints are:

```

set_input_delay -clock divclk -reference_pin clk_fwd -max 5.033 [get_ports {i}]

set_input_delay -clock divclk -reference_pin clk_fwd -min 4.022 [get_ports {i}]

```

### Output Forward Clock Delay (GPIO output)

This example shows how to set constratints for an input forward clock.

Figure 23: Forward Clock Delay (GPIO Output, Register Bypass)

The SDC constraint formulas for the foward clock delay are:

```

set_output_delay -clock <clock> -reference_pin <clkout interface name> \

-max <max calculation> <ports>

set_output_delay -clock <clock> -reference_pin <clkout interface name> \

-min <min calculation> <ports>

```

#### Reference Pin

With forward clocks, you use the <code>-reference\_pin</code> option to include the clock latency delay in the I/O constraint. The reference pin target is the pin name of the GPIO output used for the clock.

#### **Constraint Calculation**

Calculate the min and max constraints using the following equations:

```

<max calculation> = <max board constraint> + GPIO_OUT<sub>max</sub>

- < GPIO_OUT for clock pad><sub>max</sub>

<min calculation> = <min board constraint> + GPIO_OUT<sub>min</sub>

- < GPIO_OUT for clock pad><sub>min</sub>

```

The following example shows how to calculate the delays and set the constraints.

#### **Example: Constraining Output Forward Clock**

You want to constrain the o output with respect to clock clk\_fwd with a max board constraint of 2 ns and a min board constraint of 2 ns. The non-registered GPIO configuration data from the Interface Designer timing report file is:

For <GPIO\_OUT for clock pad>, use the GPIO OUT value for clk fwd.

The equations are:

```

< max \ calculation > = 2 + 2.205 - 2.205 = 2

```

$< min \ calculation > = 2 + 1.470 - 1.470 = 2$

In this example, the RTL is using a divided down clock, divclk, which is only used to drive the clk\_fwd signal off chip. Therefore, the set\_input\_delay constraint is relative to that generated clock. See Example: FPGA Forwarded Clock on page 60 for a more complete example.

The resulting constraints are:

```

set_output_delay -clock divclk -reference_pin clk_fwd -max 2 [get_ports {o}]

set_output_delay -clock divclk -reference_pin clk_fwd -min 2 [get_ports {o}]

```

## **Timing Exceptions**

Timing exceptions are constraints that override the default behavior between clocks. These constraints are:

- set false path—Cuts the path between the source and destination.

- set\_max\_delay, set\_min\_delay—Overrides the required time needed from the source to the destination for the specified paths.

- set\_multicycle\_path—Changes the clock edges used for the required timing calculation from the source to the destination.

Tip: Refer to Example: Clock-to-Clock Path with Control on page 44 for an example use case.

When working with exceptions, if the same path has more than one exception, the constraints are prioritized in the following order:

- set clock groups

- set false path

- set max delay and set min delay

- set\_multicycle\_path

### Example: Clock-to-Clock Path with Control

The following figure shows a use case in which a specific clock-to-clock path in a design can have special control logic. The path from FF1 to FF2 can have a different timing exception compared to other clock-to-clock paths in the design. You define these timing exceptions with set\_false\_path, set\_max\_delay, set\_min\_delay, or set\_multicycle\_path SDC commands.

Figure 24: Timing Exception Example

### **Understanding False Paths**

You use the set\_false\_path constraint to tell the timing analyzer not to analyze (that is, to cut) a path. For example, a clock may only toggle some of the time, and you do not want software to try to optimize timing for it.

You can cut paths between entire clock domains or individual points on the timing graph. If you want to completely cut the path between two clock domains, you should instead use the set clock groups constraint.

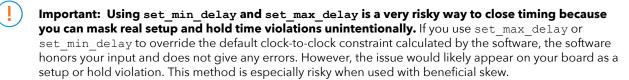

### Understanding Min and Max Delays

The set\_min\_delay and set\_max\_delay constraints override the timing requirements derived from your clock constraints. These settings tighten or relax the timing requirements for the paths. For example, you could use these constraints to try to minimize skew within a bus of signals.

Important: Using set\_min\_delay and set\_max\_delay is a very risky way to close timing because you can mask real setup and hold time violations unintentionally. If you use set\_max\_delay or set\_min\_delay to override the default clock-to-clock constraint calculated by the software, the software honors your input and does not give any errors. However, the issue would likely appear on your board as a setup or hold violation. This method is especially risky when used with beneficial skew.

### Asynchronous Paths

The set\_max\_delay and set\_min\_delay SDC commands support setting a combinational delay on an asynchronous path between ports. This path does not associate with any clock. See Figure 25: Asynchronous Data Path between Ports in Core on page 45. Clock latency and clock uncertainty are not considered for asynchronous data paths.

Figure 25: Asynchronous Data Path between Ports in Core

The constraints that represent this example are:

```

set_max_delay -from i to o <max delay>

set_min_delay -from i -to o <min delay>

```

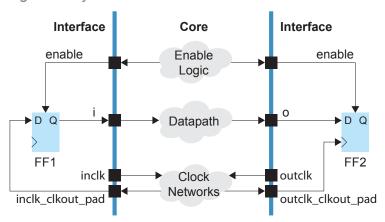

### Synchronous Paths

If you specify a maximum delay or a minimum delay for synchronous ports, you must also specify the clock domains for both -from and -to ports. In the following example, the

input and output ports of the core are connected to flipflops in the interface and special enable logic controls the clock relationship.

Figure 26: Synchronous Data Path between Ports in Core

The constraints that represent this example are:

```

create_clock -period <inclk period> -name inclk [get_ports inclk]

create_clock -period <outclk period> -name outclk [get_ports outclk]

set_input_delay -max <input max delay> -clock inclk -reference_pin <inclk_clkout_pad>

set_input_delay -min <input min delay> -clock inclk -reference_pin <inclk_clkout_pad>

set_output_delay -max <output max delay> -clock outclk -reference_pin <outclk_clkout_pad>

set_output_delay -min <output min delay> -clock outclk -reference_pin <outclk_clkout_pad>

set_max_delay -from -i -to o <max delay>

set_min_delay -from i -to o <min delay>

```

Notice that the clock out pads are reference pins for the set\_input\_delay and set\_output\_delay commands. The set\_max\_delay and set\_min\_delay commands override the default clock-to-clock constraints calculated by the system. The clock path latency and clock uncertainty are considered for synchronous ports.

### Mixed Asynchronous and Synchronous Paths

The Efinity software issues a warning and ignores the set\_max\_delay and set\_min\_delay SDC commands if one of the -to/-from ports is synchronous and the other is synchronous. The following example only has a clock associated with the -from port:

```

create_clock -name inclk -period 10.00 [get_ports inclk]

set_input_delay -clock inclk 0.1 [get_ports i]

set_max_delay 10 -from [get_ports i] to [get_ports o]

```

The software gives the following warning and ignores the set max delay command.

```

Ignore the set_max_delay (<sdc_file>:<line#>) constraint due to unconstrained

port in -to

```

The following example only has a clock associated with the -to post:

```

create_clock -name outclk -period 10.00 [get_ports outclk]

set_output_delay -clock outclk 0.2 [get_ports o]

set_max_delay 10 -from [get_ports i] -to [get_ports o]

```

The software gives the following warning and ignores the set max delay command.

```

Ignore the set_max_delay ((<sdc_file>:<line#>) constraint due to unconstrained port in -from

```

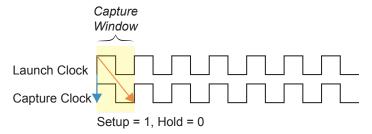

### **Understanding Multicycle Constraints**

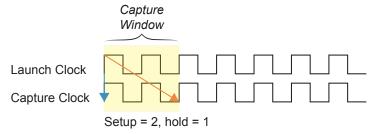

In a default single-cycle clock relationship, the two clocks are in phase and toggle together. The default setup and hold represent a one clock cycle *capture window* and is the same as setting a constraint of setup = 1 and hold = 0. The hold is checking one clock cycle before the capture clock edge. When you use the set\_multicycle\_path constraint, you are adjusting the capture window by shifting it, widening it, or both.

If you do not use a multicycle constraint, the software assumes you want the default, single-cycle relationship.

Figure 27: Default Single-Cycle Relationship

The constraints that represent the default are:

```

set_multicycle_path -setup -from a -to b 1

set_multicycle_path -hold -from a -to b 0

```

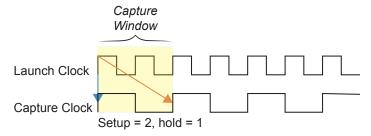

### Shifted Capture Window

To shift the capture window you use a constraint for the clock setup. The hold is still one clock cycle before the capture clock edge; the software assumes the hold is 0. Therefore, the window is still one clock cycle.

Figure 28: Setup Constraint Shifts the Capture Window

The constraints that represent this example are:

```

set_multicycle_path -setup -from a -to b 2

set_multicycle_path -hold -from a -to b 0

```

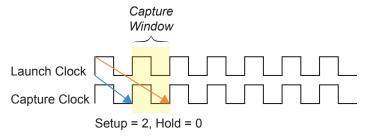

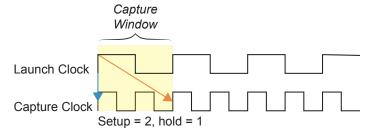

#### Shifted and Widened Window

To shift and widen the capture window you constrain the hold time as well as the setup time. A wider window allows multiple clock cycles to capture data. In the following example, the capture window is two clock cycles.

Figure 29: Setup and Hold Constraints Shift and Widen the Capture Window

The constraints that represent this example are:

```

set_multicycle_path -setup -from a -to b 2

set_multicycle_path -hold -from a -to b 1

```

If *n* is equal to *m*, then the constraint would simply be:

```

set_multicycle_path -setup -from a -to b n

set_multicycle_path -hold -from a -to b n-1

```

To shift the window by n clock cycles with a window m cycles wide, use the equations:

- setup = n

- hold = m 1

#### For example:

- n = 4, m = 3

- setup = 4

- hold = 3 1 = 2

These values give you a window that is shifted by 4 clock cycles and is 3 clock cycles wide.

```

set_multicycle_path -setup -from a -to b 4

set_multicycle_path -hold -from a -to b 2