Block RAM Wrapper Core

The BRAM Wrapper core utilizes the embedded block memory within the FPGA to optimize the utilization of memory primitives. It can be configured as Single-port RAM, Simple Dual-port RAM, True Dual-port RAM, Single-port ROM, or True Dual-port ROM. The BRAM Wrapper consists of Port A and Port B, which serve as the write and read interfaces within a shared memory space, offering a wide range of configurations.

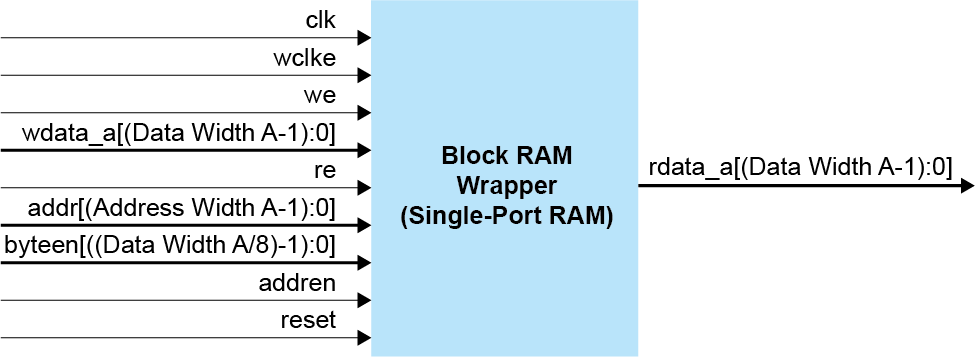

Block RAM Wrapper (Single-port RAM) Block Diagram

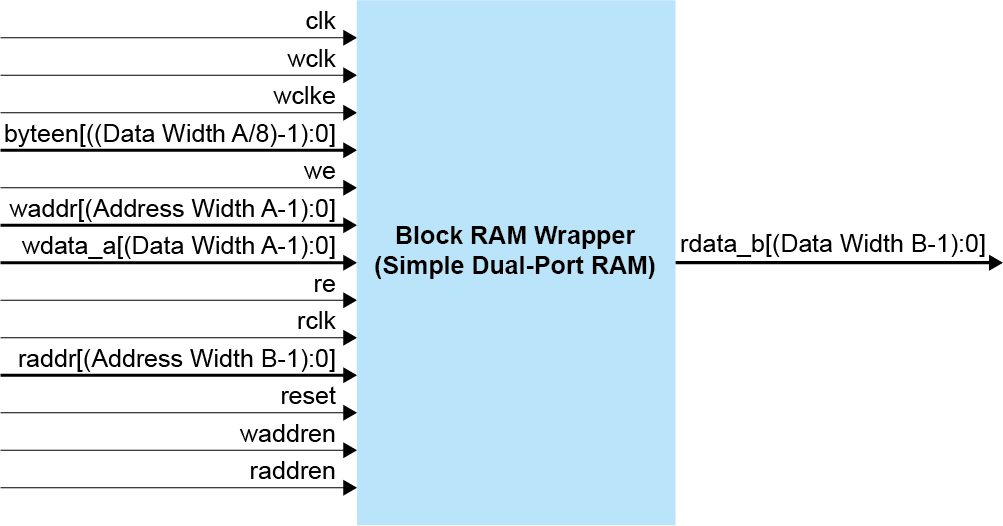

Block RAM Wrapper (Simple Dual-port RAM) Block Diagram

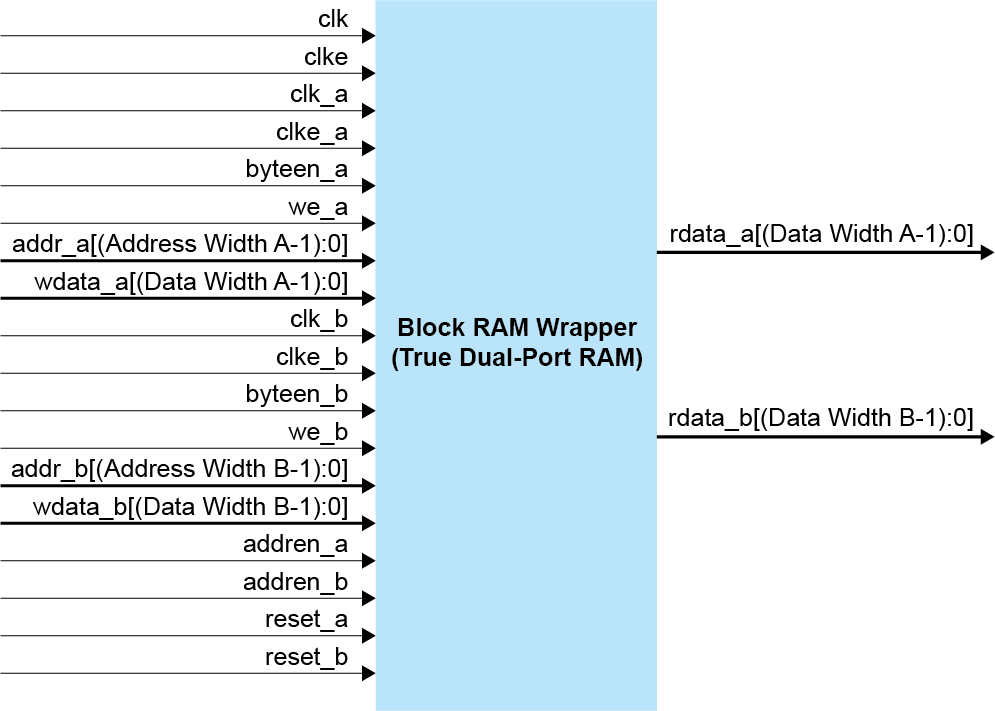

Block RAM Wrapper (True Dual-port RAM) Block Diagram

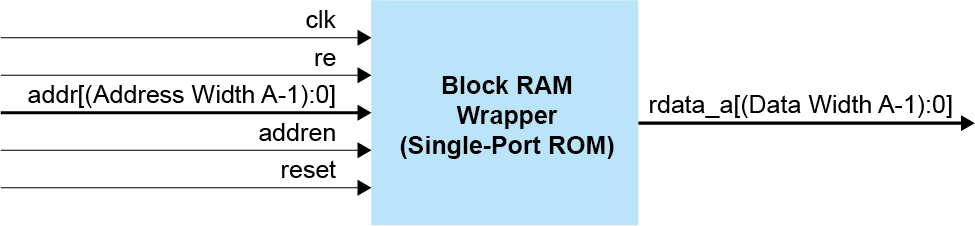

Block RAM Wrapper (Single-port ROM) Block Diagram

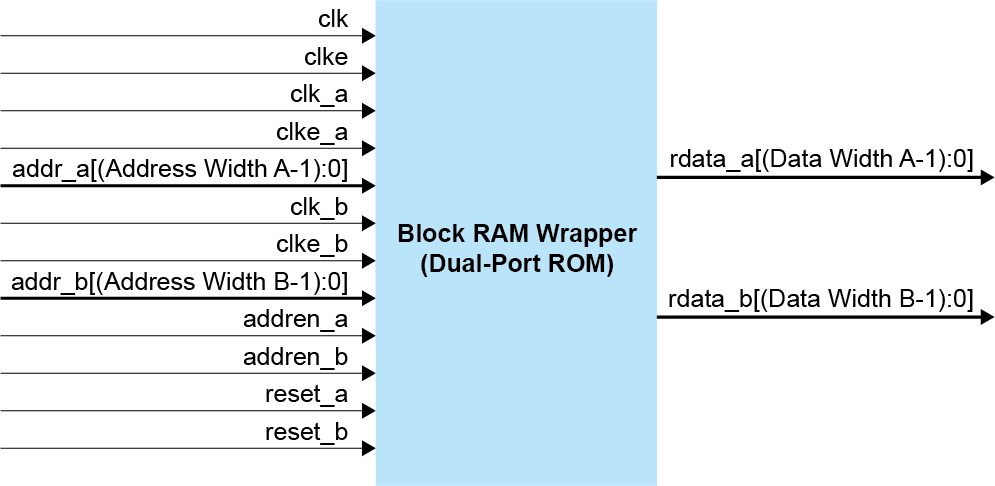

Block RAM Wrapper (Dual-port ROM) Block Diagram

Features

- Supports:

- Single-port RAM (SP RAM)

- Simple Dual-port RAM (SDP RAM)

- True Dual-port RAM (TDP RAM)

- Single-port ROM (SP ROM)

- Dual-port ROM (DP ROM)

- Supports wide range of memory address and data width (limited only by the FPGA's block RAM)

- Supports:

- Symmetric port ratio for all RAM and ROM

- Asymmetric aspect ratio for dual-port configuration (write-to-read port ratios ranging from 1:16 to 16:1).

- Selectable RAM Mode: WRITE_FIRST, READ_FIRST and READ_UNKNOWN or NO_CHANGE

- Configurable memory initialization

- Single clock and dual clock mode

- Additional option to pipeline data out for better performance

- Includes example design targeting Titanium Ti60F225 and Trion T120BGA576 Development Boards

- Testbench demonstrating memory operation simulation