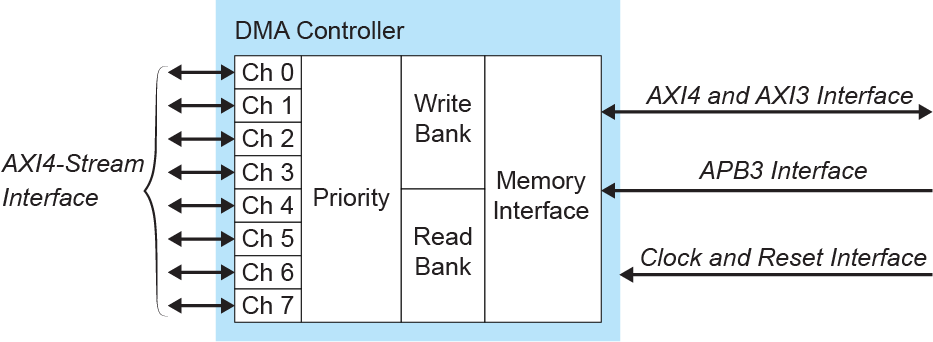

DMA Controller Core

The direct memory access (DMA) controller allows a hardware subsystem to access the main memory with minimal monitoring from the central processing unit (CPU). This reduces CPU workload when the system is required to transfer large amount of memory multiple times. The DMA Controller core provides a mechanism to transfer data between memory and AXI4-stream interface using direct mode or scatter-gather mode.

DMA Controller Block Diagram

Features

- Memory interface in AXI4 full-duplex or AXI3 half-duplex

- Programmable memory interface width

- Enhance bandwidth with hardware read and write queue

- Priority-weighted round robin scheduling

- Control and status register with APB3 interface

- Up to 8 channels of AXI4-stream interface

- Programmable stream interface width

- Supports memory-to-memory, direct, normal scatter-gather (SG), and scatter gathermode with custom descriptor list

- Includes example design targeting the Trion® T120 BGA576 Development Board

- Supports all Trion, Titanium, and Topaz FPGAs

User Guide