FIFO (Legacy) Core

The FIFO core is available in the Efinity software v2021.1.165 with patch v2021.1.165.2.19 or higher. Efinix has obsoleted the FIFO (Legacy)and replaces it with FIFO Core. You cannot migrate automatically from the FIFO (Legacy) to the FIFO core. Therefore, Efinix recommends that you use the FIFO for all new designs. You can continue to use FIFO (Legacy) with the Efinity software v2021.1.165 or lower. However, the FIFO (Legacy) will not be supported in future Efinity releases.

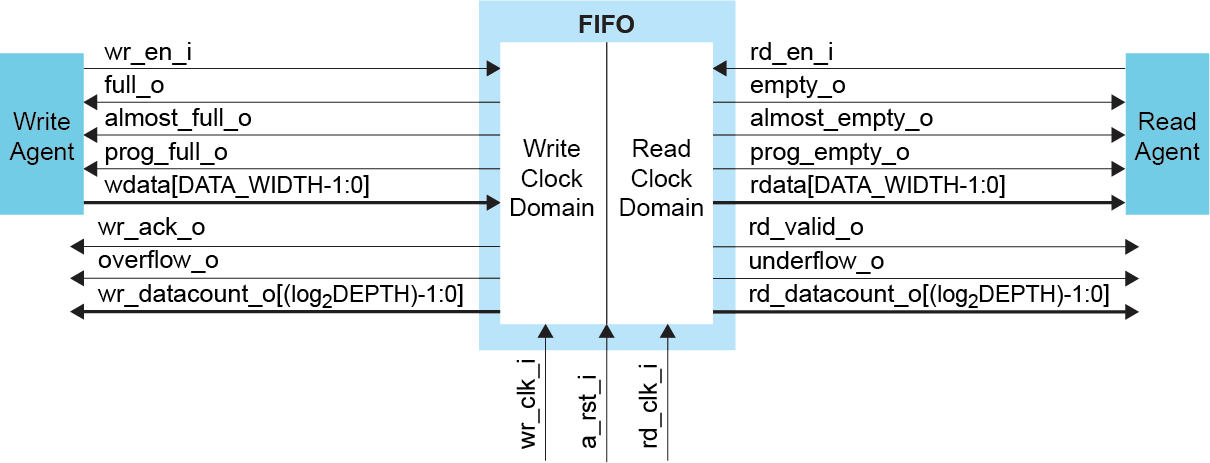

The FIFO core is a customizable first-in first-out memory queue that uses block RAM in the FPGA for storage. The core has parameters you use to create a custom instance. For example, you can set the FIFO depth, the data bus width, whether the read and write domains are synchronous or asynchronous, etc.

FIFO Controller Block Diagram

Features

- Depths up to 131,072 words

- Data widths from 1 to 1024 bits

- Symmetric read-to-write port aspect ratio

- Synchronous or asynchronous clock domains supports standard or First–Word–Fall–Through (FWFT)

- Programmable full and empty status flags, set by user-defined parameters

- Almost full and almost empty flags indicate one word left

- Configurable handshake signals

- Verilog RTL and simulation testbench

- Includes an example design targeting the Trion T20 BGA256 Development Board and Titanium Ti60 F225 Development Board

- Asynchronous clock domain FWFT read mode

- FIFO datacount to indicate how many words available in FIFO

- Recommended clock frequency for the FIFO core running C4 grade device with default setting is up to 125 MHz

- Option to exclude optional flags

- Supports all Trion and Titanium FPGAs

User Guide