HyperRAM Controller Core

HyperRAM is a memory device that uses the HyperBus protocol. The HyperRAM Controller has two width options, x8 (13 I/O pins) and x16 (22 I/O pins). This flexibility allows designers to reduce the number of traces needed on the printed circuit board and thus is ideal for scalable solutions especially in automotive, industrial, and IoT applications. The HyperRAM Controller core interfaces Titanium FPGAs with HyperRAM memories

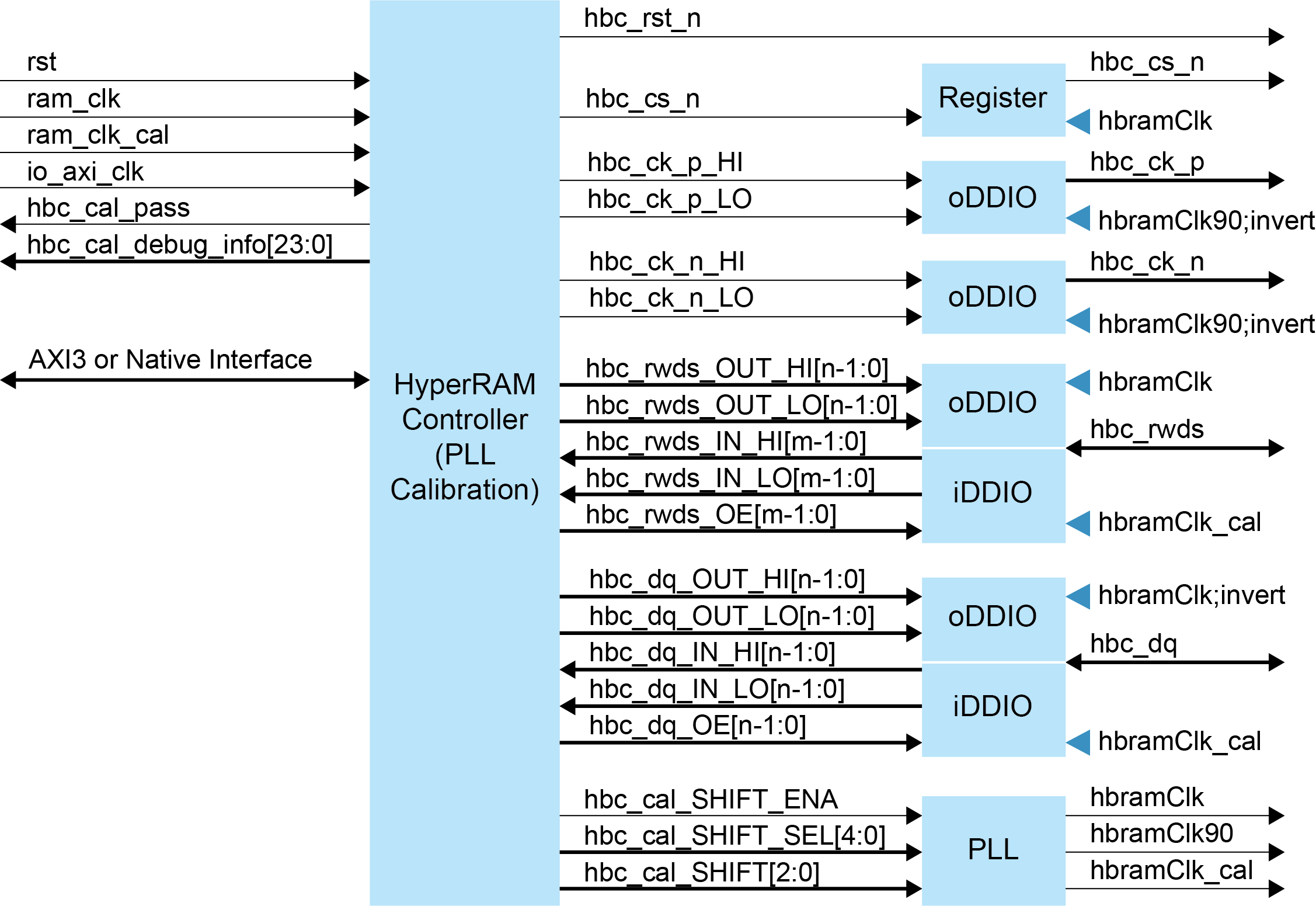

HyperRAM Controller Block Diagram

Features

- PLL auto calibration and PLL manual calibration

- Configuration periodic calibration capabilities

- x8 and x16 RAM bit widths

- Dual HyperRAM support

- Supports double-data rates of up to 800 Mbps for x16 width configuration

- Supports up to 512 Mb HyperRAM

- Linear and wrap burst transfer

- AXI3 half-duplex or native interface to core

- 32, 64, 128, and 256 bit data width

- Includes Verilog HDL RTL and simulation testbench

- Includes example designs targeting the Titanium Ti60 F225 Development Board and Titanium Ti60 F100S3F2 FPGA

User Guide