MIPI CSI-2 RX Controller Core

The MIPI CSI-2 interface, which defines a simple, high-speed protocol, is the most widely used camera interface for mobile. Adding a MIPI interface to an FPGA creates a powerful bridge to transmit or receive high-speed video data easily to/from an application processor. The MIPI CSI-2 RX Controller core allows you to perform complex video and image processing as a part of a complete system solution.

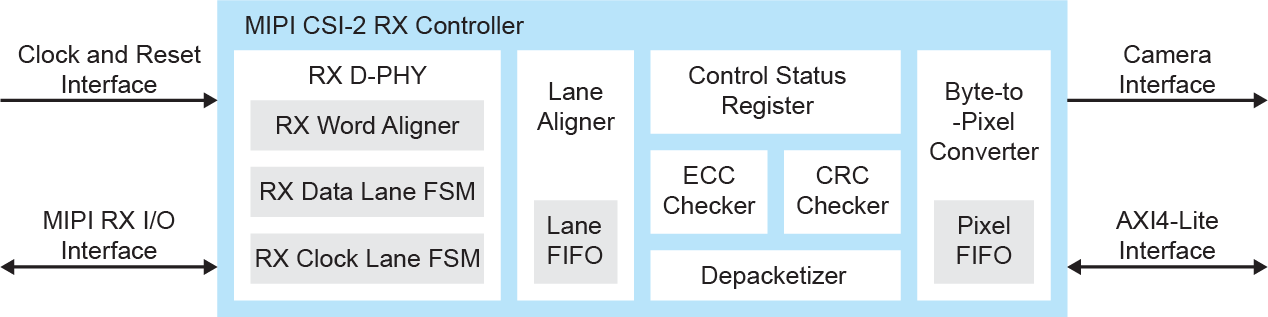

MIPI CSI-2 RX Controller Block Diagram

Features

- Configurable data lanes, 1, 2, 4, or 8 (during compilation)

- High-speed (HS) mode and Low-power (LP) mode

- Arbitrary number of payload data bytes

- HS mode byte clock frequency from 10 Mhz to 187.5 Mhz (80 Mbps to 1500 Mbps data rate)

- Continuous HS mode byte clock and discontinuous HS mode byte clock

- HS mode data width = 8

- Pixel format :

- RAW: RAW6, RAW7, RAW8, RAW10, RAW12,RAW14, RAW16, RAW20, RAW24, RAW28

- RGB: RGB444, RGB555, RGB565, RGB888

- YUV: YUV420 8-bit (legacy), YUV420 8-bit, YUV420 10-bit, YUV420 8-bit (CSPS)

- YUV420 10-bit (CSPS), YUV422 8-bit, YUV422 10-bit

- User defined 8-bit data types

- Generic 8-bit long pack

- Null, blank, and embedded 8-bit non image data

- PPI interface

- Generic frame mode and accurate frame mode

- Support end of transmission error, start of transmission sync error, control error and LP escape error

- Support control status register (CSR) for status and error assertion accessed through AXI4-Lite interface

- Supports all Titanium and Topaz FPGAs

User Guide