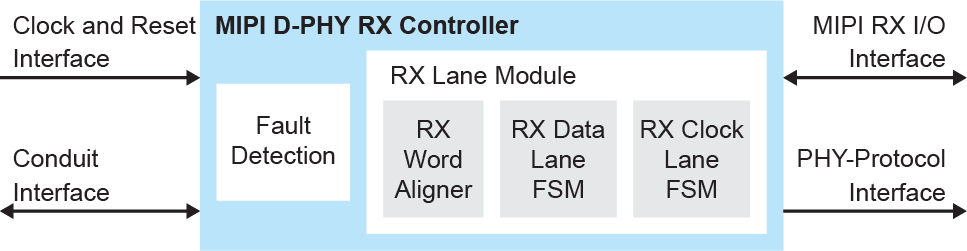

MIPI D-PHY RX Controller Core

The MIPI D-PHY is a scalable physical layer for interfacing various components such as cameras and displays to host devices. The MIPI D-PHY RX Controller core allows you to control and configure the MIPI D-PHY RX interface. You use the MIPI D-PHY RX Controller core with the Titanium HSIO pins configured as MIPI RX lanes to build a custom MIPI interface.

MIPI D-PHY RX Controller Block Diagram

Features

- 1, 2, 4, or 8 configurable data lanes

- Unidirectional (CSI) and bidirectional (DSI) data lane

- High-speed (HS) mode for data communication and low-power (LP) mode for data communication

- 100 MHz core clock frequency

- HS byte clock frequency from 10 Mhz to 187 Mhz (data rate of 80 Mbps to 1,500 Mbps)

- Continuous HS byte clock and discontinuous HS byte clock

- Supports 8 bits HS data width

- Supports D-PHY-only, D-PHY with CSI, or D-PHY with DSI

- Supports PHY protocol interface (PPI)

- Supports end-of-transmission error, start-of-transmission sync error, control error, and LP escape error

- Supports all Titanium and Topaz FPGAs

User Guide