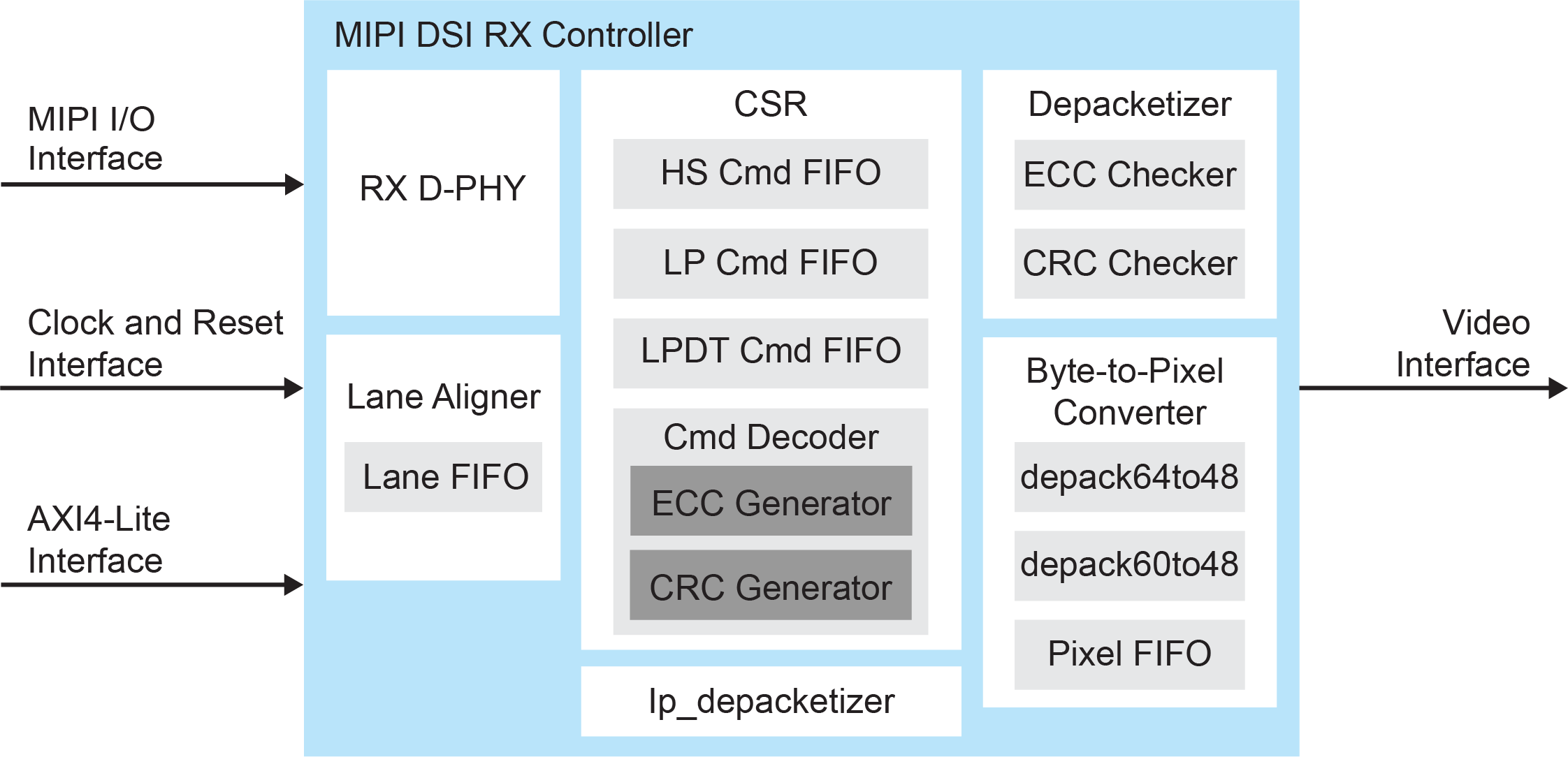

MIPI DSI RX Controller Core

The MIPI DSI specifies the physical link between the chip and display in devices such as smartphones, tablets, AR/VR headsets and connected cars. It defines a serial bus and a communication protocol between the host, the source of the image data, and the destination, for example, display peripherals. The MIPI DSI RX controller core implements the MIPI DSI interface in the FPGA and allows you to configure the related parameters.

MIPI DSI RX Controller Block Diagram

Features

- Supports 1, 2, and 4 data lanes

- Supports continuous or discontinuous clock mode

- IP core clock frequency at 100 MHz

- 8-bit HS mode data width

- HS mode byte clock frequency from 10 Mhz to 187.5 Mhz (80 Mbps to 1500 Mbps data rate)

- Includes AXI4-Lite interface for register access

- Error correction code (ECC) generation for packet headers

- Cyclic redundancy check (CRC) generation for data bytes

- Supports non-burst with sync pulses, non-burst with sync events, and burst mode

- Supports end of transmission packet

- Supports commands transmission in HS or LP mode

- Supports all Titanium and Topaz FPGAs

User Guide