SDRAM Controller Core

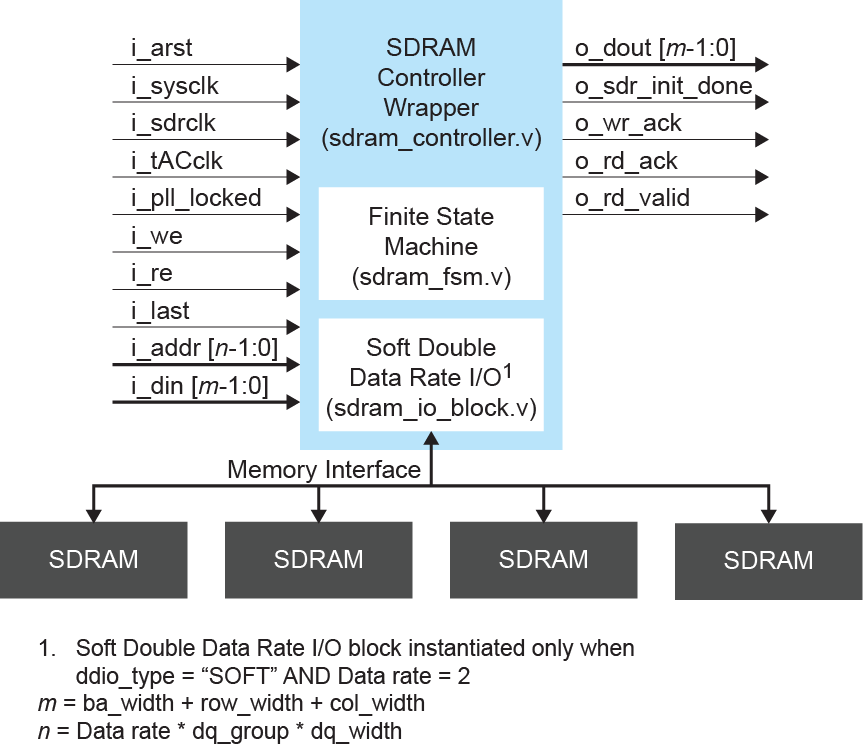

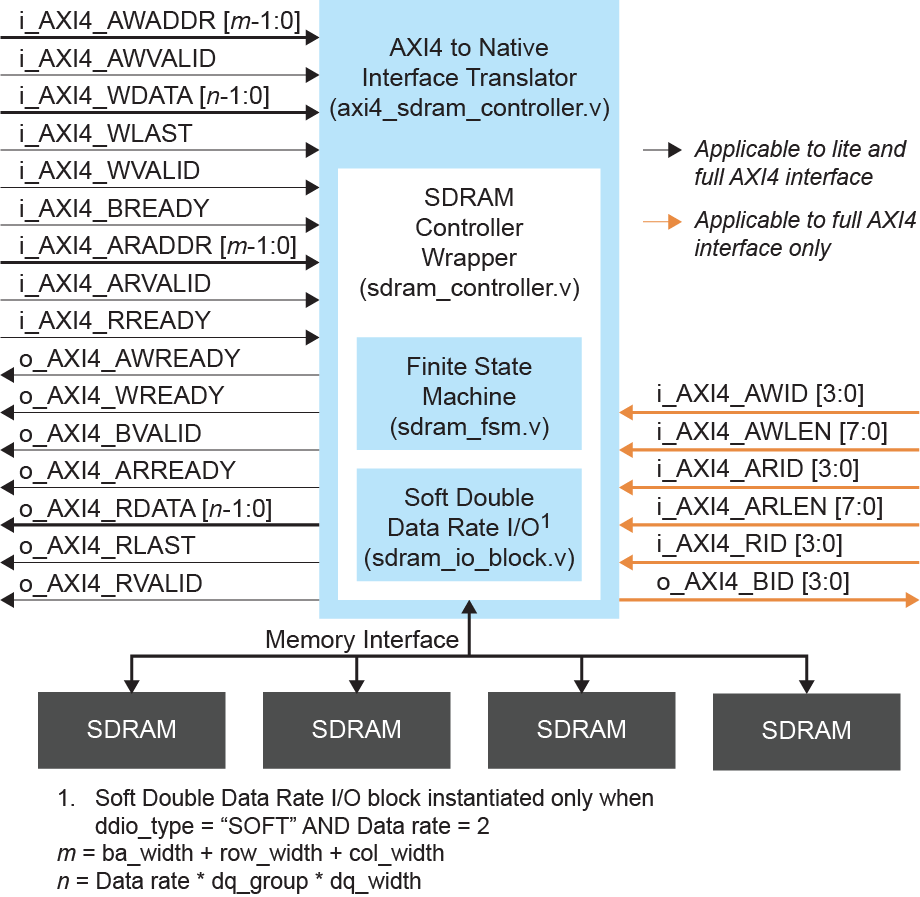

The SDRAM Controller core provides a simplified interface between a Trion® FPGA and SDRAM devices. The SDRAM Controller consists of an AXI4 to native interface translator, an SDRAM controller wrapper, a finite state machine (FSM), and a soft double data-rate block.

SDRAM Controller Core Block Diagram (Native Interface)

SDRAM Controller Core Block Diagram (AXI Interface)

Features

- Fully parameterized to be compatible with any SDRAM device

- Native mode or Advanced eXtensible Interface 4 (AXI4) mode user interface

- Half-rate or full-rate

- Memory burst length of 1

- Bank interleaving

- Random access within the same row

- Column access strobe (CAS) latency of 2 or 3

- Verilog HDL RTL and simulation testbench

- Includes an example design targeting the T20 BGA256 development board

- Supports all Trion FPGAs

User Guide