RISC-V は、非営利の RISC-V 財団によって管理されている、RISC の設計思想に基づいたオープン標準の命令セット・アーキテクチャ (ISA) です。このモジュール型 ISA は、基本命令セットとオプションの拡張セットが用意されています。RISC-V は無償かつオープンソースであるため、世界中で人気が高まっています。現在、商用、オープンソースを含めて 65 以上の RISC-V コアが利用可能です。

エフィニックス (Efinix) は、Charles Papon 氏が開発した VexRiscv コアをベースの RISC-V SoC を用意しています。2018年の RISC-V SoftCPU コンテストで 1 位を獲得した VexRiscv コアは、拡張機能を持つ ISA RISCV32I を採用した 32 ビット CPU で、パイプラインステージ、構成変更が可能な機能セットを備えています。それぞれの SoC には、RISC-V プロセッサ、メモリ、各種 I/O、ユーザ機能を追加するためのインターフェイスが搭載されています。そのため、組み込みコンピューティングとユーザ定義アクセラレータを含むシステムを、同一の Titanium および Trion® FPGA で簡単に設計することができます。

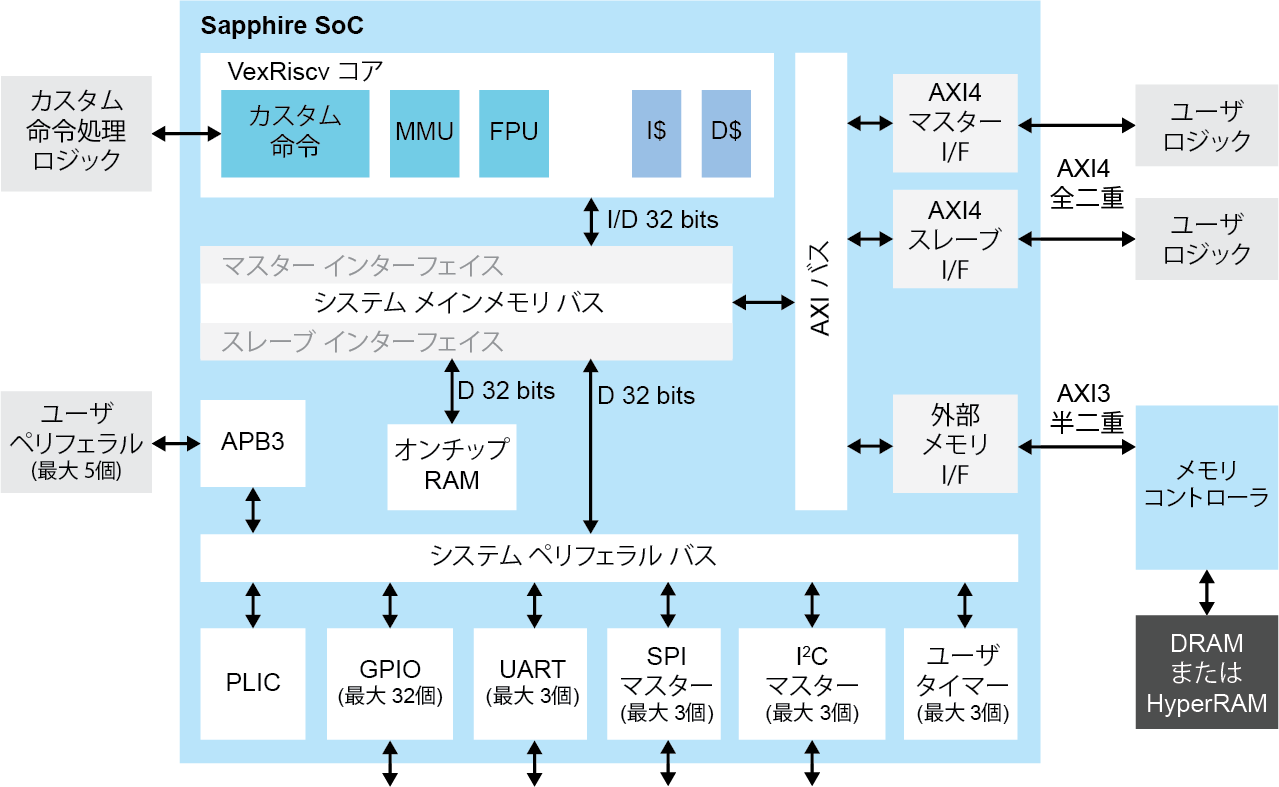

Sapphire SoC

ユーザー設定可能な高性能 SoC で、オプションでメモリコントローラを搭載可能。Efinity IP マネージャで必要なペリフェラルを選択し、SoC を構成することができます。この Sapphire SoC の柔軟性は、様々な組み込みアプリケーションに最適です。

- VexRiscv コア - 6 つのパイプラインステージ (フェッチ、インジェクタ、デコード、実行、メモリ、ライトバック)、割込処理、例外処理

- システムクロック: 20 ~ 400 MHz

- オンチップ RAM: 4 ~ 512 KB (SPI FLASH用のブートローダーを含む)

- DDR または HyperRAM メモリコントローラ

- メモリサイズサポート: 4 MB ~ 3.5 GB

- ユーザ設定可能な外部メモリバス周波数

- 外部メモリアクセスのための半二重 AXI3 インターフェイス (最大 256 ビット)

- 400 MHz DDR クロック周波数、800 Mbps

- 200 MHz HyperRAM クロック周波数、400 Mbps

- ユーザロジック用の AXI マスタチャネル (最大 2 系統)

- ユーザロジック用の AXI スレーブチャネル (1 系統)

- 浮動小数点ユニット

Efinity IP マネージャ v2021.1 以降でサポート

- Linux 用の MMU (メモリ マネジメント ユニット)

- カスタム命令セット (様々な機能を実現するための 1,024 ID)

- RISC-V アトミック拡張機能、Compressed 命令 (オプション)

- APB3 ペリフェラル:

- GPIO 最大 32 本

- I2C マスタ 最大 3 個

- Clint Timer

- PLIC

- SPI マスタ 最大 3 個 (最大 25 MHz)

- Timer 最大 3 個

- UART 最大 3 個

- APB3 ユーザペリフェラル 最大 5 個

Sapphire SoC は、32ビット RISC-V プロセッサで、命令キャッシュ (最大 8 方向、1 ~ 32 KB)、データキャシュ (最大 8 方向、1 ~ 32 KB)、オンチップ RAM (4 ~ 512 KB)、、各種ペリフェラル (1 ~ 5 の APB3 スレーブペリフェラルと AXI スレーブ が1つ) で構成されています。動作周波数は、20 ~ 400 MHz の範囲で設定可能です (実性能は、ユーザデザインの最大動作周波数[fMAX]に依存します)。SoC は、I2C (1 ~ 3 個)、UART (1 ~ 3 個)、ユーザタイマー (1 ~ 3 個)、SPI マスタ (1 ~ 3 個) に加え、浮動小数点ユニット (FPU)、カスタム命令インターフェイス、Linux用メモリマネジメントユニット (MMU) も用意されています。

デフォルトの構成では、最大 256 ビットの半二重 AXI バスにより、DDR コントローラまたは HyperRAM コントローラと通信します。

- DDR コントローラ—このコアは、Trion FPGA のハード DDR DRAM インターフェイスを使用して、外部 DRAM モジュールをリセットします (Trion FPGA の DDR インターフェイスと DDR モジュールをリセットし、再初期化します)

- HyperRAM コントローラ—このコアは、HyperRAM メモリモジュールを制御します

Efinity® ソフトウェアの IP マネージャにより、SoC のカスタマイズが可能です。

パッケージ内容

各 RISC-V SoC パッケージには、ハードウェアとソフトウェア関連の全てのファイルおよびアプリケーション開発を容易にするためのオープンソースのソフトウェアサンプルが含まれています。これらのパッケージを使用することにより以下のことが可能です:

- エフィニックス開発キットをターゲットとした Sapphire RISC-V SoC を使用した RTL 設計およびサンプルからユーザーアプリケーションへの適用

- サンプルプロジェクトを用いたソフトウェア開発環境の設定、ユーザープロジェクトの作成、API の使用

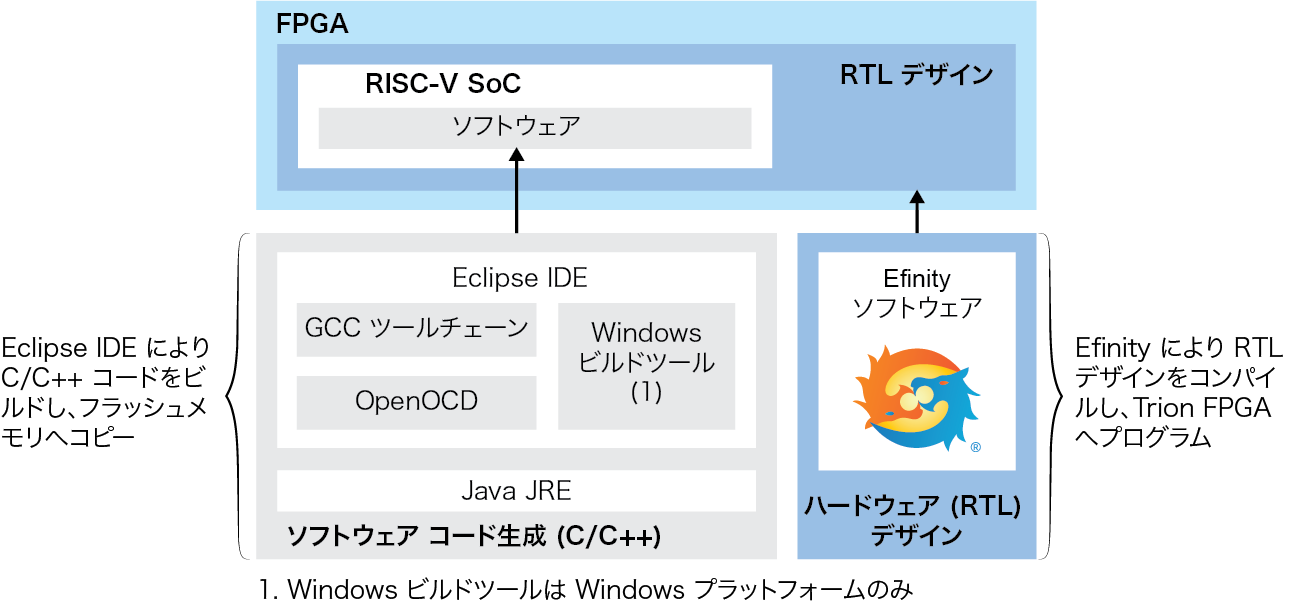

SoC デザイン フロー

ハードウェア

- SoC RTL ファイル

- SoC テストベンチ

- 開発キット用のサンプルデザイン

- Efinity ソフトウェアでサポート

ソフトウェア

- BSP (ボード サポート パッケージ)

- リンカー スクリプト

- SoC ヘッダーファイル

- OpenOCD 設定ファイル

- ソフトウェア サンプル集

- Efinity ソフトウェアでサポート

SDK

- Eclipse IDE (プロジェクトやソフトウェアの管理)

- GCC コンパイラ

- OpenOCD デバッガ

- Windows ビルドツール (Windows OS のみ)

- サポートセンターよりダウンロード

Efinity ソフトウェア サポート

Efinity® ソフトウェアは、すべての RISC-V SoC をサポートしており、RTL デザインからビットストリーム生成 (論理合成、配置配線、デバッグ、タイミング解析を含む) までの完全なツールフローを提供します。ソフトウェアには、プロジェクトの設定、ツールフローの実行、および結果の表示を視覚的に操作するための GUI (グラフィカル・ユーザ・インターフェイス) およびコマンドライン・フロー、Tcl コマンド・コンソールが用意されています。ソフトウェアで生成されたビットストリーム・ファイルにより Trion FPGA をコンフィギュレーションします。ソフトウェアは、Verilog HDL 言語と VHDL 言語をサポートしています。