RISC-V SoC Accelerator Framework

Our Quantum® accelerators are pre-defined, structured "containers" that streamline your acceleration efforts. They are sockets that let you incorporate a hardware accelerator quickly and easily. Software engineers can pull out hot spots in their code, areas they want to target for acceleration. Then hardware engineers can develop an accelerator and drop it into the pre-built Quantum® accelerator. The result is standard calls to a standard hardware accelerator.

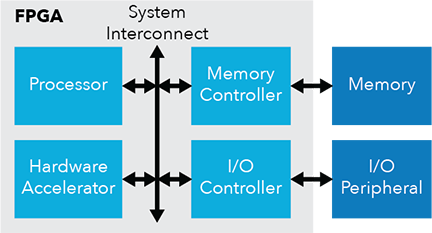

Efinix has created a RISC-V-based, open infrastructure for you to develop your accelerator function without having to create everything from scratch. This accelerator socket has specific inputs and outputs to the accelerator function, RISC-V processor, DMA controller, and other processing blocks. You can drop your accelerator function into this open framework, which includes pre-defined chip-level inputs, outputs, and system interconnects. This framework minimizes your design effort and creates a scalable, repeatable way for you to design quickly and easily.

- Natural and intuitive design

- Pre-defined hardware accelerator socket

- Repeatable and scalable

- Modular building blocks for a flexible system architecture

- Easily portable to specialized use cases

Our RISC-V SoC Accelerator Framework comprises domain-specific accelerator frameworks for edge vision, AIoT, and other applications. Benefits of this framework include:

- Ready-to-deploy domain-specific I/O peripherals and interfaces, including software drivers, hardware controllers, pre-processing, and post-processing blocks.

- Established flow to handle data transfers between sensors, memory, and functional blocks through direct memory access (DMA).

- Domain-specific embedded software functions and hardware accelerator modules supporting flexible hardware/software co-design.

- Modular building blocks for highly flexible design. Depending on your use case, you can swap in new functional blocks or bypass unneeded ones to achieve higher system performance.

- RISC-V processor controls the overall FPGA hardware system and performs general computations.

- Easy porting of the design for specific use cases, speeding time to market.

Framework Block Diagram