Trion® T35 FPGAs

The T35 FPGA features the high-density, low-power Efinix® Quantum® fabric wrapped with an I/O interface in a small footprint package for easy integration. T35 FPGAs support mobile, consumer, and IoT edge markets that need low power, low cost, and a small form factor. These FPGAs have hardened MIPI CSI-2 controllers with independent TX/RX. Additionally, they have hardened DDR DRAM controller that supports DDR3, LPDDR3, and LPDDR2. T35 FPGAs:

- Some packages have hardened MIPI CSI-2 interfaces for video and camera applications

- Feature a hardened DDR DRAM interface for accessing off-chip memory devices

- Have LVDS pins that operate at 800 Mbps per lane

- Are built on a low-power 40 nm process

- Feature high-performance I/O supporting 1.8, 2.5, and 3.3 V single-ended I/O standards and interfaces

- Provide flexible on-chip clocking

- Have device configuration options including a standard SPI and JTAG interfaces

- Fully supported by the Efinity® software, an RTL-to-bitstream compiler

Applications

Mobile, Consumer, IoT, Edge

Features

| Logic elements: | 31,680 |

| RAM (Kbits): | 1475.00 |

| RAM (blocks): | 288 |

| Multipliers (18 x 18): | 120 |

Documents

Available T35 FPGAs

| Ordering Code |

Package | Pins | GPIO | PLLs | Osc. | SPI Flash (Mbit) | LVDS TX |

LVDS RX |

MIPI TX |

MIPI RX |

DDR | Temp. Grade |

Speed Grade |

Where to Buy |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| T35F256C3 | FBGA | 256 | 191 | 7 | – | – | 10 | 18 | – | – | – | C | 3 | DigiKey Find distributor |

| T35F256C4 | FBGA | 256 | 191 | 7 | – | – | 10 | 18 | – | – | – | C | 4 | DigiKey Find distributor |

| T35F256I4 | FBGA | 256 | 191 | 7 | – | – | 10 | 18 | – | – | – | I | 4 | DigiKey Find distributor |

| T35F324C3 | FBGA | 324 | 130 | 7 | – | – | 20 | 26 | 2 | 2 | x8, x16 | C | 3 | DigiKey Find distributor |

| T35F324C4 | FBGA | 324 | 130 | 7 | – | – | 20 | 26 | 2 | 2 | x8, x16 | C | 4 | DigiKey Find distributor |

| T35F324I4 | FBGA | 324 | 130 | 7 | – | – | 20 | 26 | 2 | 2 | x8, x16 | I | 4 | DigiKey Find distributor |

| T35F400C3 | FBGA | 400 | 230 | 7 | – | – | 20 | 26 | – | – | x8, x16 | C | 3 | DigiKey Find distributor |

| T35F400C4 | FBGA | 400 | 230 | 7 | – | – | 20 | 26 | – | – | x8, x16 | C | 4 | DigiKey Find distributor |

| T35F400I4 | FBGA | 400 | 230 | 7 | – | – | 20 | 26 | – | – | x8, x16 | I | 4 | DigiKey Find distributor |

Available Packages

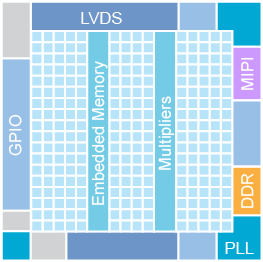

T35 FPGA

BGA324

(12 x 12 mm, 0.65 pitch)

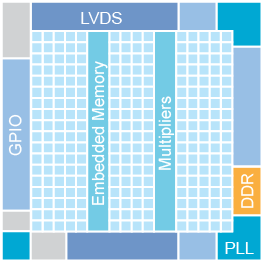

BGA400

(16 x 16 mm, 0.8 pitch)

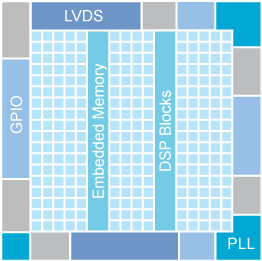

BGA256

(13 x 13 mm, 0.8 pitch)

Use Cases

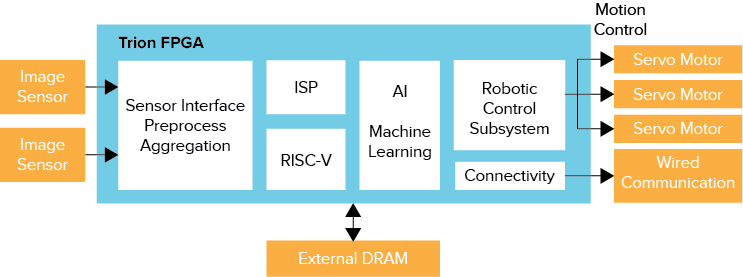

Collaborative Robot

In the industrial market, collaborative robots combine machine vision and robotics, both of which require low latency, high compute, and low power. The FPGA can implement an AI or dedicated algorithm to process real time results, making decisions and driving control of the motors based on those inputs.