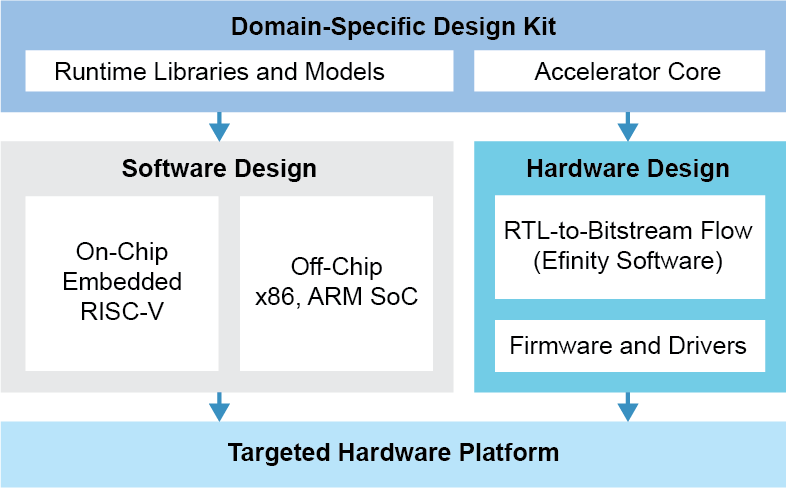

Complementing this enhanced hardware versatility, the RAP initiative also delivers an intuitive approach to system design and software partitioning. A standardized hardware accelerator interface lets you leverage the RISC-V cores available on Efinix FPGAs. You can build hardware accelerators in the FPGA, resulting in more intuitive hardware/software partitioning, reduced time to market, and dramatically improved system performance.

Solving Challenges at the Edge

With the global datasphere approaching 175 ZB by 2025, the need for devices to collect, capture, transform, transmit, and otherwise process all of this data is overwhelming. Devices now reside everywhere, potentially in harsh environments with limited access to power or consistent bandwidth. They need to process large quantities of data locally and securely in real time, only take up a small space, and consume very little power. These constraints are driving the need for innovative solutions. Adding to the problem, shrinking process geometries results in exponentially increasing costs. Designers cannot rely on the next-generation silicon to meet their time-to-market needs.

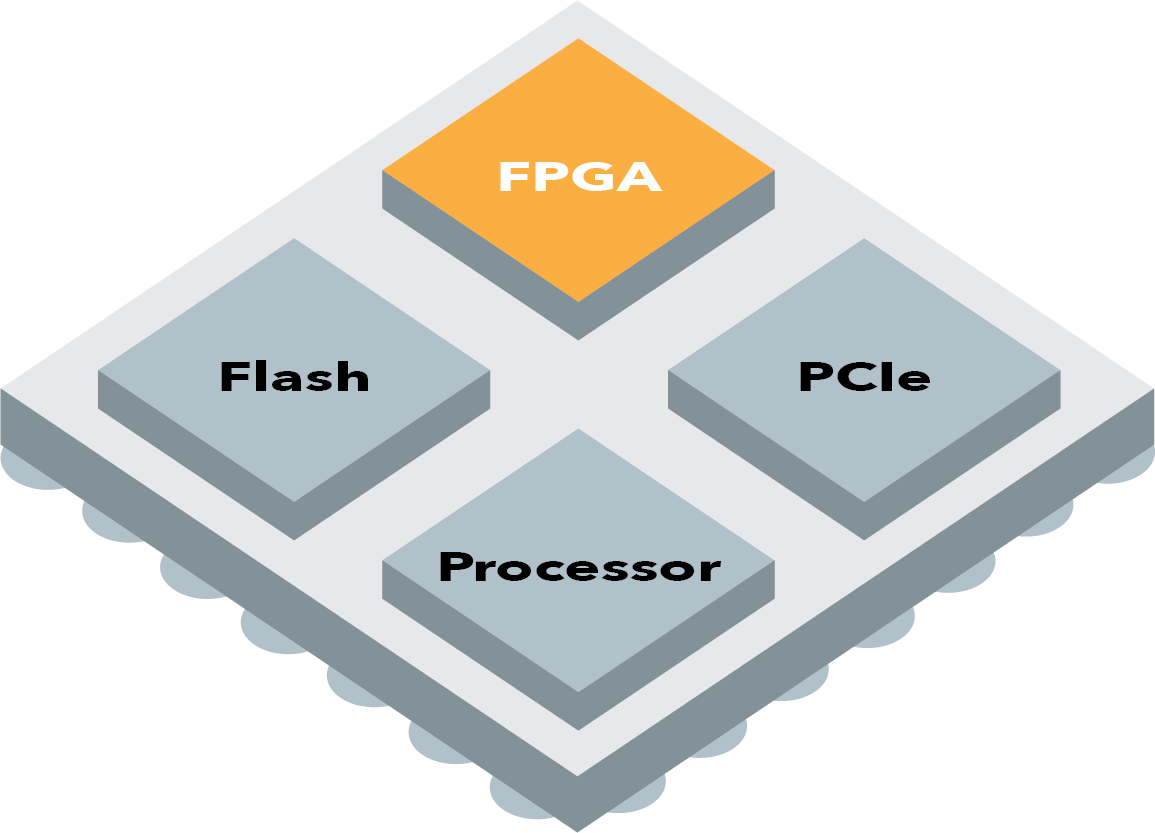

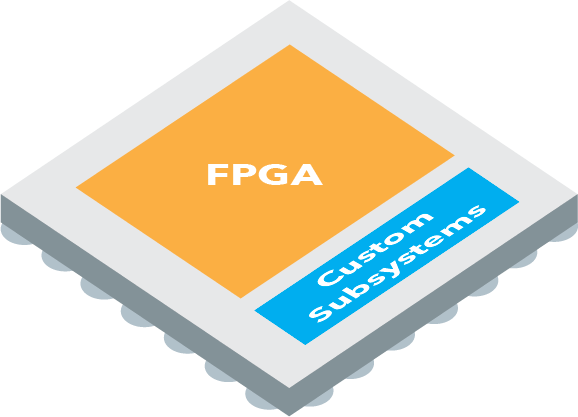

Applications at the edge are vast, chaotic, diverse, and evolving—and they need configurable, optimized solutions. By design, FPGAs are programmable, even after they are incorporated into a deployed product, which helps you adapt to changing requirements flexibly. At the edge, FPGAs can provide complete systems to solve real-world problems. The RAP initiative addresses two key problems for edge applications: the physical delivery mechanism and I/O diversity required in edge devices and the need to accelerate data processing within a framework of conventional software-driven applications and control structures.

Read white paper: Accelerating Edge Computing with Trion FPGAs

Watch Webinar Recording: Accelerating Edge Computing with FPGAs