Trion® T8 FPGAs

The T8 FPGA features the high-density, low-power Efinix® Quantum® fabric wrapped with an I/O interface in a small footprint package for easy integration. T8 FPGAs support mobile, consumer, and IoT edge markets that need low power, low cost, and a small form factor. T8 are available in quite small packages with really low power because they are produced on a special low voltage process. These FPGAs are more a minimalistic offering for hand held, control plane, and other functions. T8 FPGAs:

- Are built on a low-power 40 nm process

- Feature high-performance I/O supporting 1.8, 2.5, and 3.3 V single-ended I/O standards and interfaces

- Provide flexible on-chip clocking

- Have device configuration options including a standard SPI and JTAG interfaces

- Fully supported by the Efinity® software, an RTL-to-bitstream compiler

- Optional mask option, that allows you to eliminate the configuration device, thereby saving space and costs

Applications

Mobile, Consumer, IoT, Edge

Features

| Logic elements: | 7,384 |

| RAM (Kbits): | 122.88 |

| RAM (blocks): | 24 |

| Multipliers (18 x 18): | 8 |

Documentation

Development Kit

Available T8 FPGAs

| Ordering Code |

Package | Pins | GPIO | PLLs | Osc. | SPI Flash (Mbit) | LVDS TX |

LVDS RX |

MIPI TX |

MIPI RX |

DDR | Temp. Grade |

Speed Grade |

Buy Now |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| T8F49C2 | FBGA | 49 | 33 | 1 | 1 | – | – | – | – | – | – | C | 2 | DigiKey Find distributor |

| T8F49I2 | FBGA | 49 | 33 | 1 | 1 | – | – | – | – | – | – | I | 2 | DigiKey Find distributor |

| T8F81C2 | FBGA | 81 | 55 | 1 | 1 | – | – | – | – | – | – | C | 2 | DigiKey Find distributor |

| T8F81I2 | FBGA | 81 | 55 | 1 | 1 | – | – | – | – | – | – | I | 2 | DigiKey Find distributor |

| T8Q144C3 | LQFP | 144 | 97 | 5 | – | – | 6 | 6 | – | – | – | C | 3 | DigiKey Find distributor |

| T8Q144C4 | LQFP | 144 | 97 | 5 | – | – | 6 | 6 | – | – | – | C | 4 | DigiKey Find distributor |

| T8Q144I4 | LQFP | 144 | 97 | 5 | – | – | 6 | 6 | – | – | – | I | 4 | DigiKey Find distributor |

Available Packages

T8 FPGA

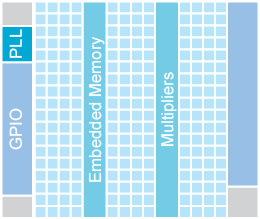

BGA49

(3 x 3 mm, 0.4 pitch)

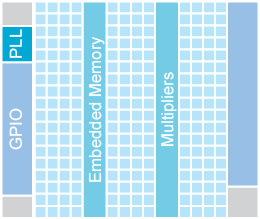

BGA81

(5 x 5 mm, 0.5 pitch)

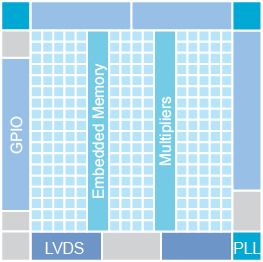

LQFP144

(20 x 20 mm, 0.5 pitch)

Use Cases

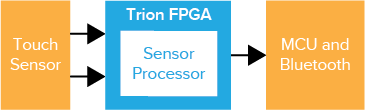

Capacitive Stylus

The algorithm in T8 FPGA acts as a coprocessor by computing location data based on sensor inputs. Data from that algorithm is then passed to MCU and quickly transferred to base unit controlling the display. Speed, low power, and small footprint were important attributes in this case.

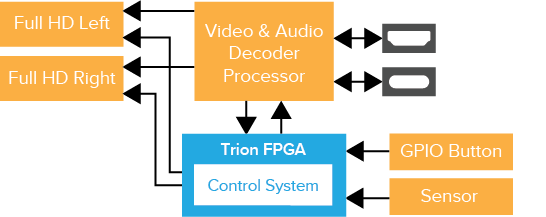

Virtual Reality Headset

This is a multi-sensor aggregation application that computes movement data based on inputs from user inputs and other location sensors. The algorithm in the T8 provides control functions. Small form factor and low power are important for this design.