Software Highlights

![]()

Projects

Project management to keep your design files organized

![]()

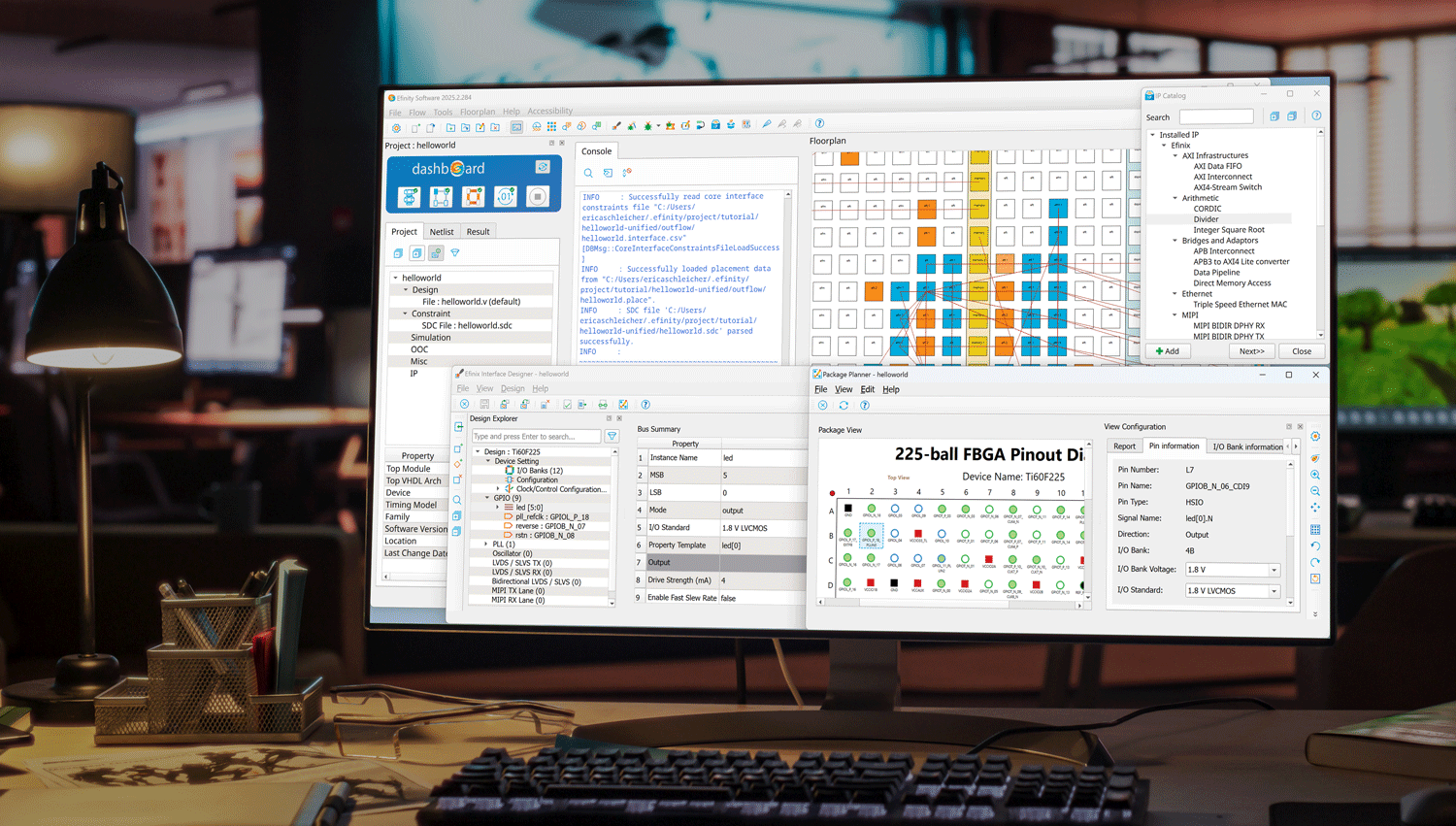

Dashboard

Easy-to-use dashboard to run the tool flow automatically or manually

![]()

Language Support

Verilog HDL, SystemVerilog, and VHDL

![]()

Interface Designer

Constrain logic and assign pins to blocks in the device periphery

![]()

IP Manager

Configure and add buildling blocks to your project

![]()

Floorplan Viewer

Visualize your design's placement

![]()

Netlist Viewer

Displays and analyzes your design's netlist

![]()

Timing Browser

Browse timing and perform static timing analysis

![]()

Simulation

Supports simulation flows using the ModelSim, NCSim, or free iVerilog simulators

![]()

BRAM Initial

Content Updater

Update initial BRAM without performing a full compile

![]()

Python API

Use scripts to build your design's interface

![]()

Package Planner

Assign logic to package pins and view the pinout graphically

![]()

Hardware Debugger

Integrated hardware Debugger with Logic Analyzer and Virtual I/O debug cores

![]()

Programmer

GUI and command-line Programmer to configure your FPGA

![]()

JTAG SVF Player

Sends JTAG command to an FPGA

![]()

Bitstream Authentication and Encryption

Sign and/or encrypt bitstreams