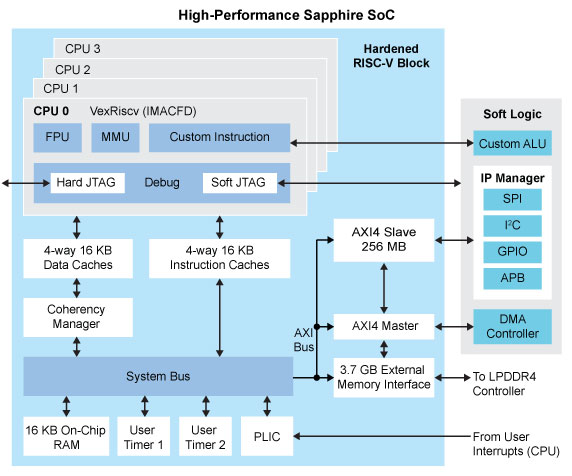

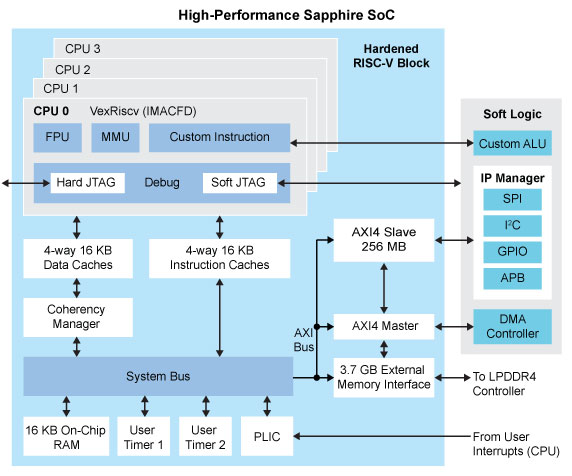

High-Performance Sapphire SoC

High-Performance Sapphire RISC-V SoC は、メモリ コントローラ、ダイレクトメモリアクセスチャネル、カスタム命令、I/O デバイスなど、さまざまな周辺機器をサポートするインターフェイスを提供します。Efinity® IP マネージャで SoC を構成することにより、使用するインターフェイスを選択できます。

- 4コア VexRiscv:6つのパイプラインステージ (フェッチ、インジェクター、デコード、実行、メモリ、およびライトバック)、割り込み、およびマシンモードによる例外処理

- 最大1GHzのシステムクロック周波数

- SPIフラッシュ用のブートローダーを備えた 16KB オンチップRAM

- LPDDR4x用のメモリコントローラ

- 3.7GB のメモリモジュールサイズをサポート

- ユーザーが構成可能な外部メモリバス周波数

- 外部メモリと通信するための 1つの全二重 512ビット AXI4 インターフェイス

- 1つのAXIマスターチャネル:ユーザーロジック用、データ幅128ビット

- 1つのAXIスレーブチャネル:ユーザーロジック用

- 各コアには以下が含まれます:

- 4-way 16KBデータおよび命令キャッシュ

- 浮動小数点ユニット(FPU)

- Linuxメモリ管理ユニット(MMU)

- さまざまな機能を実行するための 1,024個の ID を備えたカスタム命令インターフェイス

- 整数、乗算、アトミック、圧縮、1桁および 2桁の浮動小数点などの RISC-V 拡張機能をサポート

- 8つのハードウェアブレークポイントを備えた JTAG デバッグモジュール

- ペリフェラル:

この SoCは特定のFPGAでのみ利用可能です。サポートされているデバイスの詳細については、Titanium および Topaz を参照してください。

Read data sheet >

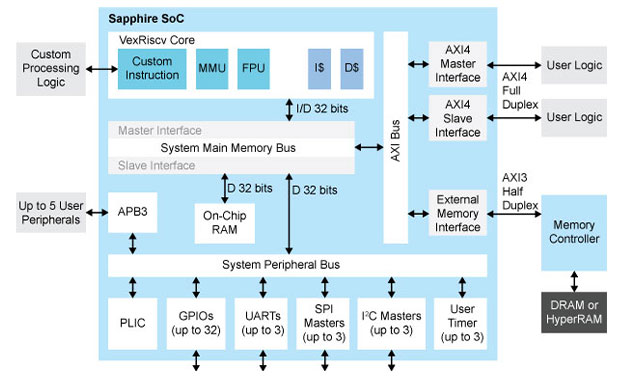

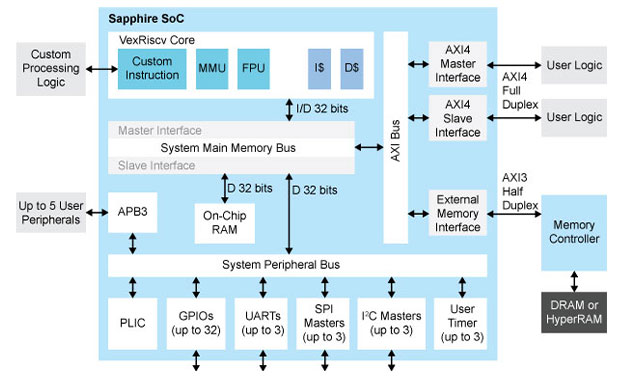

Sapphire SoC

Sapphire SoC は、さまざまな組み込みアプリケーションをサポートする、汎用的でユーザーが構成可能なソフトコア SoC です。

- 最大4コアのユーザーが自由に構築可能なVexRiscvプロセッサコア:6つのパイプラインステージ (フェッチ、インジェクター、デコード、実行、メモリ、およびライトバック)、割り込み、およびマシンモードによる例外処理

- 20 ~ 400MHzのシステムクロック周波数

- 1 ~ 512KBのオンチップRAM:SPIフラッシュ用ブートローダ

- DDR3、LPDDR4x、または HyperRAM 用メモリコントローラ

- 4MB ~ 3.5GB のメモリモジュールサイズをサポート

- ユーザー設定可能な外部メモリバス周波数

- 外部メモリと通信するための 1つの半二重 AXI3 インターフェイス (最大512ビット) または 1つの全二重 AXI4 (最大512ビット)

- 400MHz DDR3 クロック周波数、800Mbps

- 1089MHz LPDDR4x クロック周波数、2178Mbps

- 250MHz HyperRAM クロック周波数、500Mbps

- 最大2つの AXI マスターチャネル:ユーザーロジック用の、データ幅32 ~ 512

- 1つのAXIスレーブチャネル:ユーザーロジック用

- オプション:マルチウェイ命令およびデータキャッシュ

- オプション:浮動小数点ユニット (FPU)

- オプション:Linux メモリ管理ユニット (MMU)

- オプション:さまざまな機能を実行するための 1,024個の ID を持つカスタム命令インターフェイス

- アトミックや圧縮などのオプションの RISC-V 拡張機能をサポート

- APB3 周辺機器:

- 最大32個のGPIO

- 最大3個のI2Cマスター

- Clintタイマー

- プラットフォームレベルの割り込みコントローラ(PLIC)

- 最大3個のSPIマスター

- 最大3個のユーザータイマー

- 最大3個のUART 115,200ボーレート

- 最大5個のスレーブユーザーペリフェラル

- 最大8個のユーザー割り込み

この SoC は、すべての Trion® FPGA(T4を除く)、すべての Titanium® FPGA、および Topaz® FPGAで利用できます。

Read data sheet >

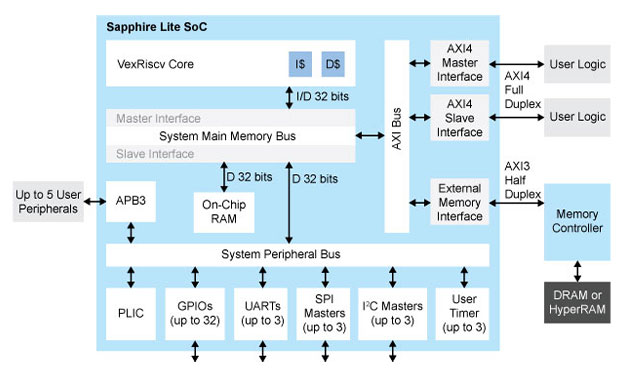

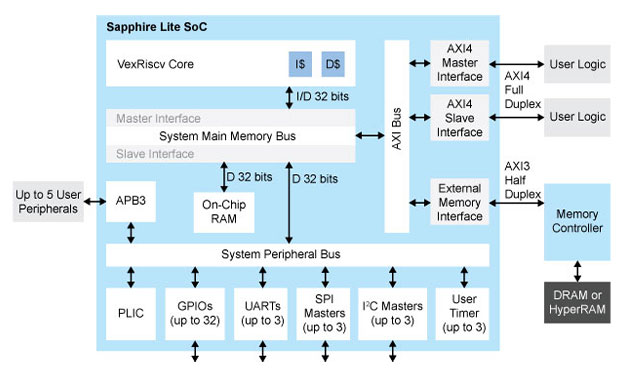

Sapphire Lite SoC

Sapphire Lite SoC はフットプリントが最も小さく、マイクロコントローラアプリケーションに最適です。最小のバリエーションでは、使用する LE は4K未満です。このスリム化されたバージョンは、処理能力が少しだけ必要な場合に最適です。

サポートされている機能

- シングルコア VexRiscvプロセッサ(RV32IM):6つのパイプラインステージ (フェッチ、インジェクター、デコード、実行、メモリ、およびライトバック)、割り込み、およびマシンモードによる例外処理

- ロジック4K LE未満でも使用可能

- カスタマイズ可能なオンチップ RAM、キャッシュ、APB3周辺機器

- FreeRTOSを実行可能

- 外部メモリと通信するための1つの半二重 AXI3 インターフェイス (最大512ビット) または 1つの全二重 AXI4 (最大512ビット)

- 内部メモリで0.7DMIPS/MHz

制限事項

- カスタム命令なし

- アトミック拡張なし

- 圧縮拡張なし

- FPUなし

- MMUなし(Linuxサポートなし)

この SoC は、すべての Trion® FPGA(T4を除く)、すべての Titanium® FPGA、および Topaz® FPGA で利用できます。

Read data sheet >