Ti35, Ti60, Ti90, Ti120, and Ti180 shipping now in production volumes. Find a distributor

![]()

小型パッケージ

Titanium™ FPGAは、わずか 3.5mm x 3.4mm WLCSP の極小パッケージを備え、高度に統合されるアプリケーション向けに設計されています。

![]()

ハードコントローラ

ハード化されたMIPI D-PHY と DDR DRAMコントローラーは、IoT・温度カメラ・産業用カメラ・ロボティクス・スマートデバイスをサポートします。

![]()

SEU検出

Titanium™ デバイスはデバイスの整合性を監視します。ランダムなSEUイベントから回復するアプリケーションを設計でき、稼働時間を最大限に確保します。

![]()

ビットストリームのセキュリティ

ビットストリーム認証は不要な改ざんを防止し、ビットストリーム暗号化は設計の安全性を保証します。

当社のTitanium™ FPGAは、その名の由来となった物性に基づいて名付けられています。堅牢性を備え、要求の厳しいアプリケーション向けに設計されています。Titanium FPGAは実際にはチタンは含まれていませんが、この名称は同モデルの力強さ、卓越した性能、そしてさらに向上した実力を示すものです。

Titanium™製品は、多くの多様な市場における幅広い用途に合わせて設計されています。 これらの市場のいくつかは、長期製品ライフサイクルが特徴で、一度大量生産されると、部品表の仕様やコンポーネントの変更に抵抗があります。 Efinixではそれを理解しており、お客様の製品ライフサイクルを通してサポート対象製品を安定的に供給することに尽力しています。 当社は、少なくとも 2045 年まで、Titanium™ファミリ FPGA をサポートすることをお約束しています。製品ライフ サイクルの詳細については、最寄りの営業担当者にお問い合わせください。

Titanium™ FPGA は、今日の産業アプリケーションにおいて増大する量のデータを処理するためのセンサーフュージョン、データ分析、リアルタイム モーター制御などの用途に最適です。

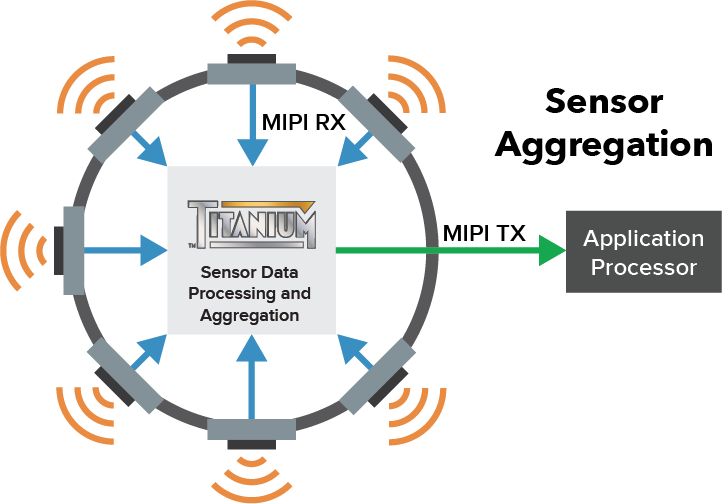

カメラやセンサーは至る所に設置され、大量のデータを生成しています。これらをどのように集約し処理すればよいのでしょうか?

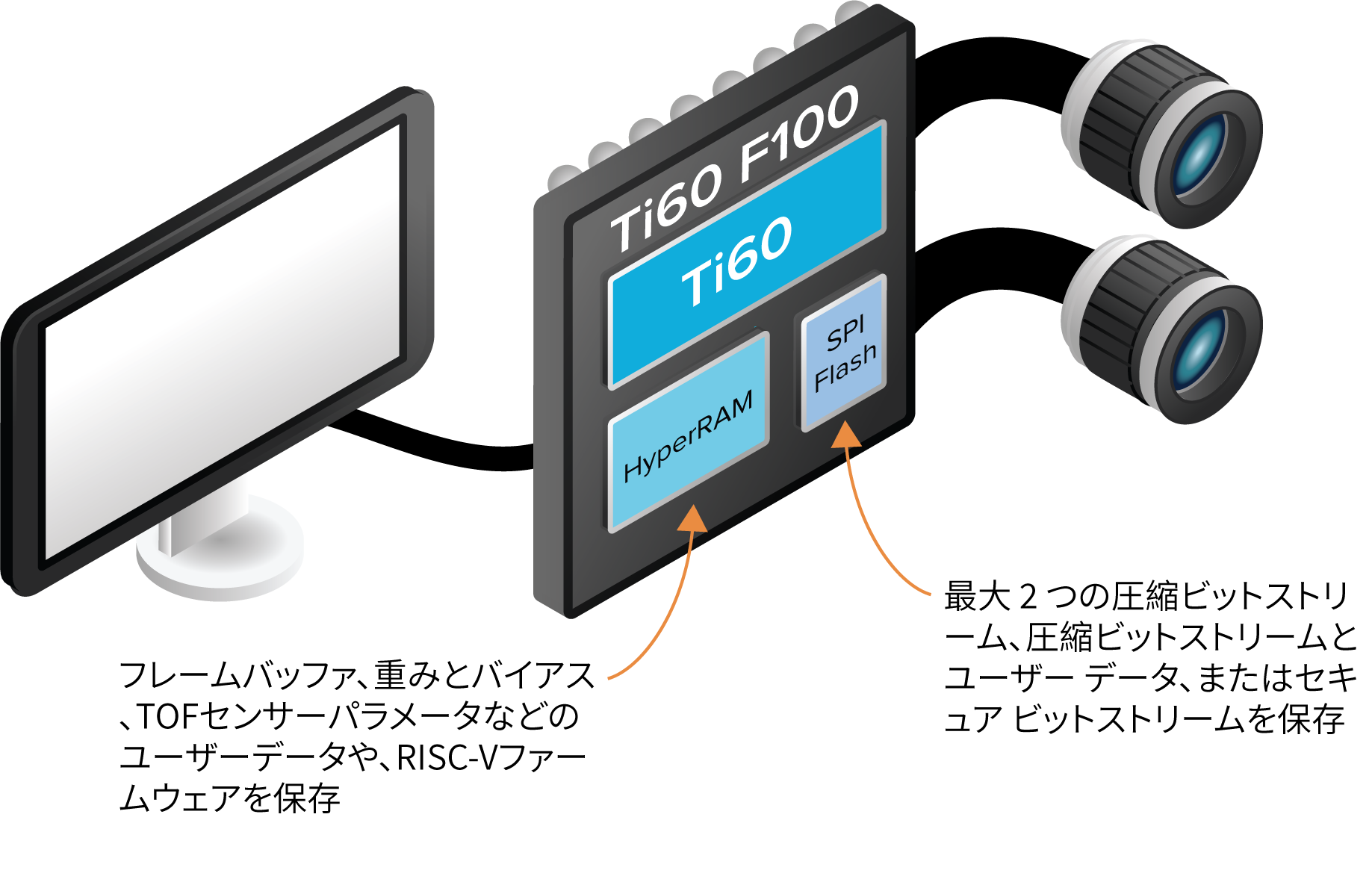

Ti90 およびそれ以上のサイズの FPGA には、高速リンク用の 2.5G MIPI インターフェース ハードブロックが搭載されています。 Titanium™ の高速 I/O (HSIO) ピンは、数多くのシングルエンドおよび差動 I/O 規格に対応しています。通常の GPIO または LVDS ペアとして使用できます。また、最大1.5 Gbps の MIPI RX/TX レーンとしても使用できます。

これらの HSIO ピンは、ユーザーが自由に設定できるため、システムのニーズに合わせて組み合わせることができます。HSIO ピンは、MIPI CSI-2 プロトコルを使用して、カメラやセンサーからデータを収集し、アプリケーションプロセッサに送信したり、DSI プロトコルを使用して、画像をディスプレイに送ることもできます。Efinity® ソフトウェアには、D-PHY、CSI-2、DSIの IP コアが含まれており、MIPI ベースのシステムをより簡単に設計することができます。

各パッケージで利用可能なリソース (例:I/O 数、PLL 数、ハードブロック数) の詳細については、FPGA データシートまたは Titanium™ Selector Guide のパッケージ リソース表を参照してください。

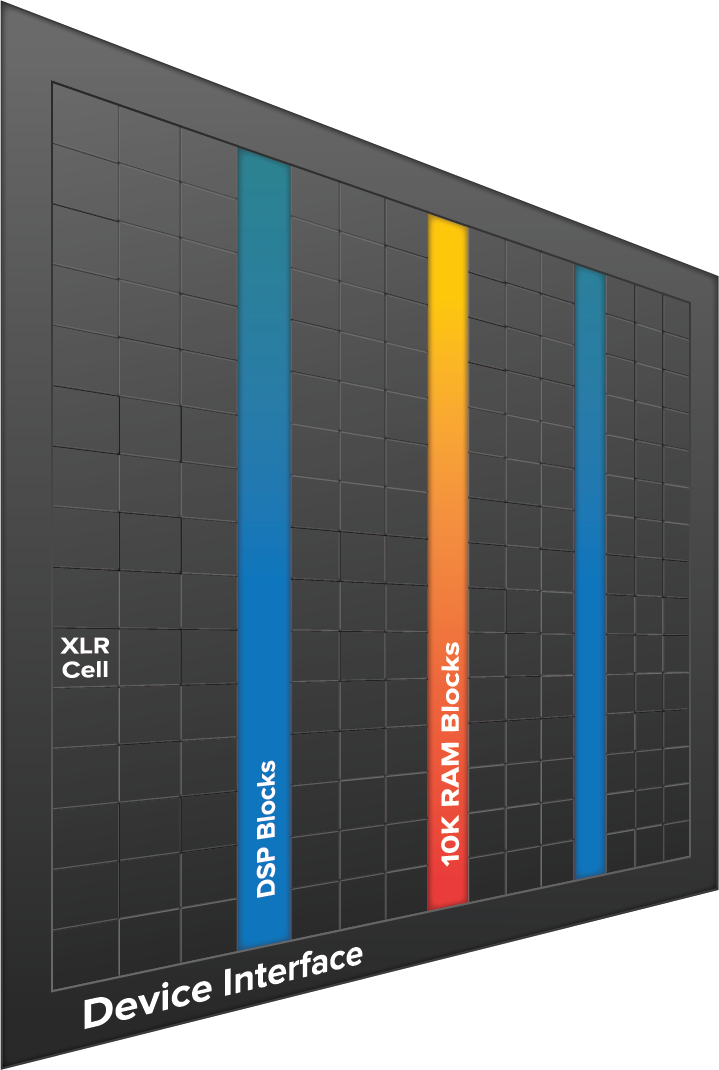

演算性能が強化された革新的な Quantum® コンピューティング・ファブリックによる Titanium™ FPGA は組み込みハードウェア・アクセラレーション等のアプリケーションに最適です。3.5万 ~ 200万ロジック・エレメント (LE) をサポートし、エフィニックス RISC-V SoC との互換性により、アクセラレーション機能を用いる組み込み演算システムを非常に小さなチップの中に実装することができます。

マシンビジョン、ドローン、ロボット、自動車、監視カメラなどのモバイル機器やその影響を受ける機器では、動画がいたるところに存在しています。Titanium™ FPGA には、小型パッケージが用意されているため、エッジ・システムに簡単に処理能力を追加することができます。3.5 x 3.4 mmの 64 ボール ウェハレベル CSP パッケージは、センサーやカメラのすぐ隣に配置できるほど小型であり、ソースレベルでの低遅延ビジョンおよび AI ワークロードを実現します。