![]()

小型パッケージ

Trion FPGAは、わずか 4.5mm x 3.6mm WLCSP の最小パッケージを備え、高度に統合されるアプリケーション向けに設計されています。

![]()

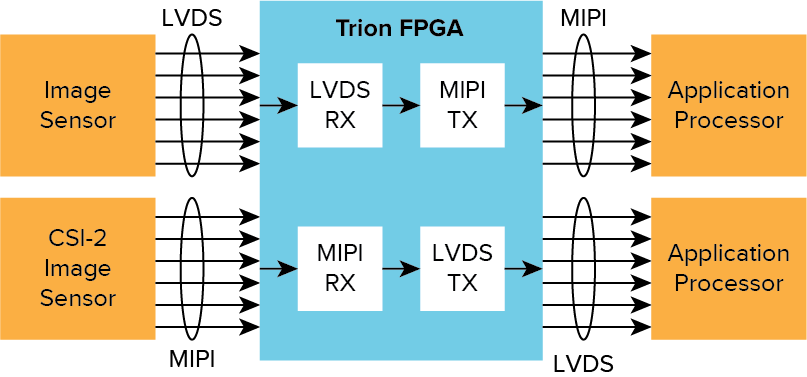

MIPI CSI-2 コントローラ

一般的な MIPI CSI-2インターフェイスのハードコントローラーは、IoT、温度カメラ、産業用カメラ、ロボティクス、スマート デバイスをサポートします。

![]()

DDR DRAM コントローラ

DDR DRAM ハードコントローラーで処理データを保存できます。

All devices shipping in production volumes. Find a distributor

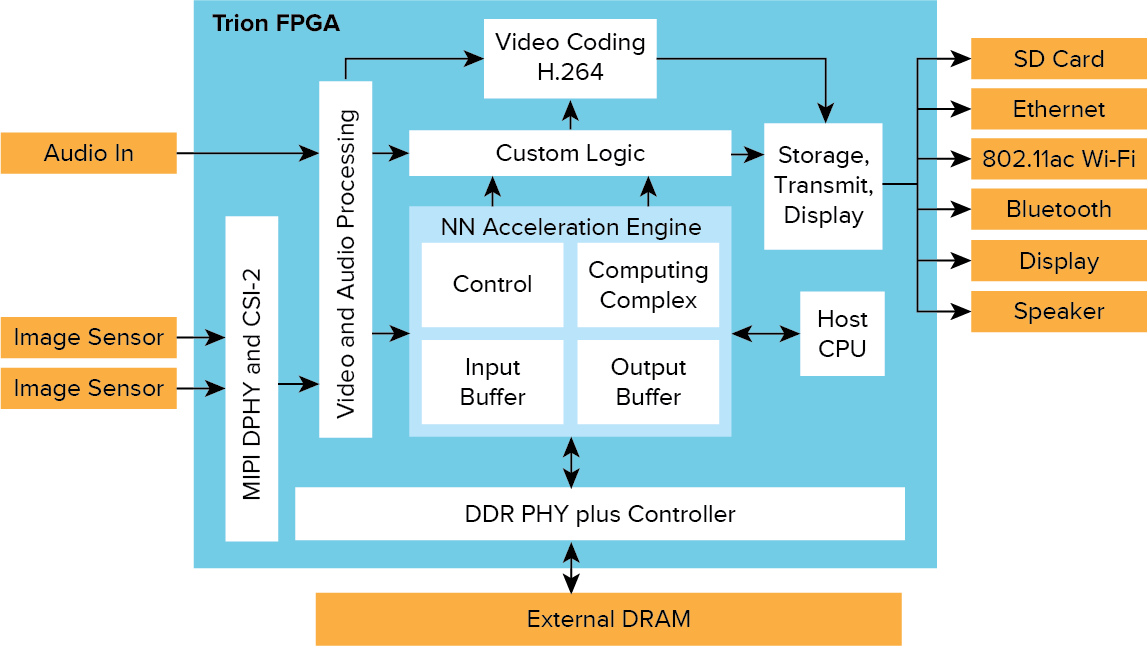

この Trion® プラットフォームは SMIC 40nm LL プロセスで製造され、4,000 ~ 20万ロジック・エレメント (LE) のロジック集積度を持ち、GPIO、PLL、発振器、MIPI、DDR、LVDS などの標準インターフェイスを内蔵しています。Trion FPGA は、汎用カスタム・ロジック市場 (モバイル、IoT、一般的なコンシューマ製品、産業機器、医療機器など) をターゲットにしています。また、エッジデバイスでの深層学習や演算アクセラレーターのような急成長している市場もサポートします。

![]()

小型パッケージ

Trion FPGAは、わずか 4.5mm x 3.6mm WLCSP の最小パッケージを備え、高度に統合されるアプリケーション向けに設計されています。

![]()

MIPI CSI-2 コントローラ

一般的な MIPI CSI-2インターフェイスのハードコントローラーは、IoT、温度カメラ、産業用カメラ、ロボティクス、スマート デバイスをサポートします。

![]()

DDR DRAM コントローラ

DDR DRAM ハードコントローラーで処理データを保存できます。

Trion製品は、多くの多様な市場における幅広い用途に合わせて設計されています。 これらの市場のいくつかは、長期製品ライフサイクルが特徴で、一度大量生産されると、部品表の仕様やコンポーネントの変更に抵抗があります。 Efinixではそれを理解しており、お客様の製品ライフサイクルを通してサポート対象製品を安定的に供給することに尽力しています。 当社は、少なくとも 2045 年まで、Trionファミリ FPGA をサポートすることをお約束しています。製品ライフ サイクルの詳細については、最寄りの営業担当者にお問い合わせください。

Trion FPGAは、今日の産業アプリケーションにおいて増大する量のデータを処理するためのセンサーフュージョン、データ分析、リアルタイム モーター制御などの用途に最適です。

Trion T4、T8、T13、および T20 FPGA は、49 ボール、81 ボール、および 144 ボールの FineLine BGA などの小型パッケージで提供されており、迅速な市場投入を必要とする小型の低電力アプリケーションに最適です。 モバイル、IoT、ウェアラブル、AR/VR の接続、その他の消費者向け製品で使用できます。

| パッケージ | ピッチ (mm) |

サイズ (mm) |

GPIO (1) | PLLs | SPI Flash (Mbit) |

LVDS Pairs TX, RX |

MIPI CSI-2 TX, RX (1) |

DDR DRAM (1) |

T4 | T8 | T13 | T20 | T35 | T55 | T85 | T120 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 49ボール FBGA | 0.4 | 3x3 | 33 | 1 | ||||||||||||

| 80ボール WLCSP | 0.4 | 4.5x3.6 | 33 | 3 | 1, 1 | |||||||||||

| 81ボール FBGA | 0.5 | 5x5 | 55 | 1 | ||||||||||||

| 100-pin LQFP |

0.5 | 14x14 | 65 | 5 | 16 | 4, 4 | ||||||||||

| 144-pin LQFP |

0.5 | 20x20 | 97 | 5 | 6, 6 | |||||||||||

| 169ボール FBGA |

0.65 | 9x9 | 73 | 5 | 8, 12 | 2, 2 | ||||||||||

| 256ボール FBGA | 0.8 | 13x13 | 195 | 5 | 13, 13 | |||||||||||

| 324ボール FBGA | 0.65 | 12x12 | 130 | 7 | 20, 26 | 2, 2 | x8, x16 | |||||||||

| 400ボール FBGA | 0.8 | 16x16 | 230 | 7 | 20, 26 | x8, x16 | ||||||||||

| 484ボール FBGA | 0.8 | 18x18 | 256 | 8 | 40, 40 | x16, x32 | ||||||||||

| 576ボールl FBGA | 0.65 | 16x16 | 278 | 8 | 52, 52 | 3,3 | x16, x32 |

Trion T13、T20、T55、T85、および T120 FPGA は、GPIO や LVDS ピンを多数備えているため、高帯域幅インターフェイスのブリッジや I/O 拡張に役立ちます。これらの I/O 豊富な FPGA は、放送、ディスプレイ、制御、オートメーション、ロボティクスなどのアプリケーションをサポートします。

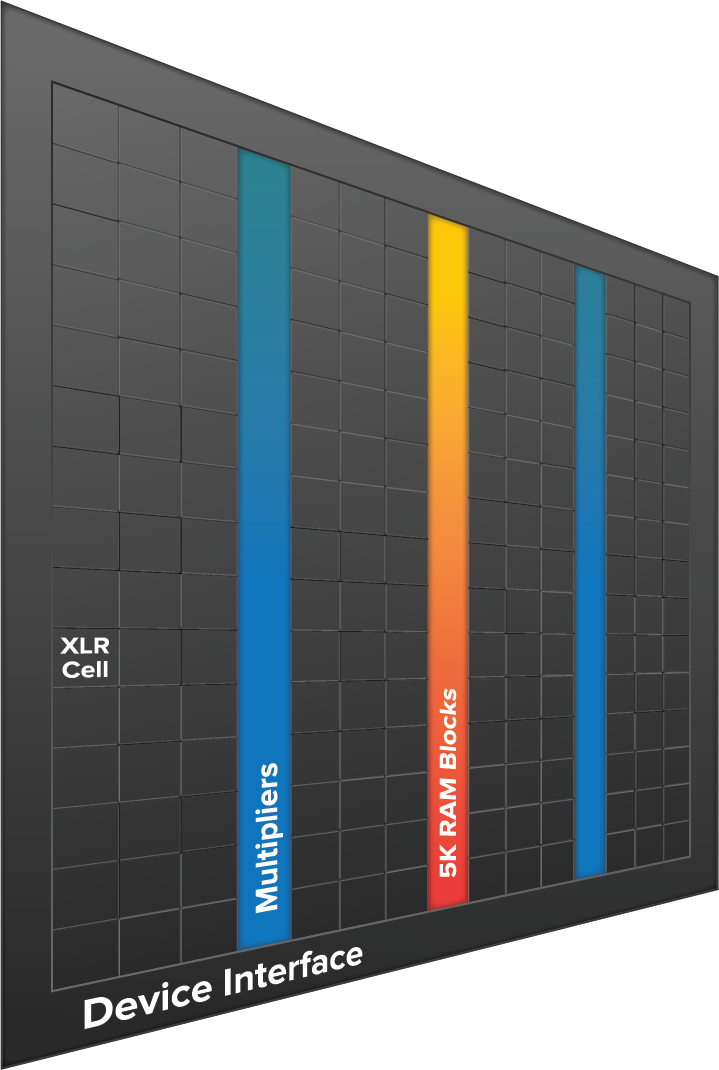

エフィニックス (Efinix®) Trion® プログラマブル・プラットフォームは、当社の Quantum® テクノロジをベースに構築されており、従来の FPGA 製品と比較して、パワー・パフォーマンス・エリアに大きな優位性をもたらします。Trion FPGA は、プログラマブル・ロジックと Quantum テクノロジを使用したルーティング・ファブリックを特徴としています。このファブリックは、外周に I/O インターフェイスを持ち、モバイルや IoT などの多くの大量生産アプリケーションで必要とされる小型パッケージ要求を満足します。ロジックおよびルーティングに加えて、内蔵メモリと乗算器ブロック (または DSP ブロック) が含まれています。

データシート

DDR3/LPDDR3 メモリ・インターフェイス、MIPI インターフェイス、ソフト・プロセッサ・システム (RISC-V など) を搭載したTrion T13、T20、T35、T55、T85 および T120 FPGAを使用することで、スマートホーム製品、監視カメラ、業務用カメラ、ハイエンド・インテリジェント・システムなどのアプリケーション向けの完全なシステム・ソリューションを構築することができます。Trion FPGA の中核をなす Quantum® コアの微細なアーキテクチャは、演算を要する機械学習アルゴリズムやディープ・ニューラル・ネットワークの構築に最適です。