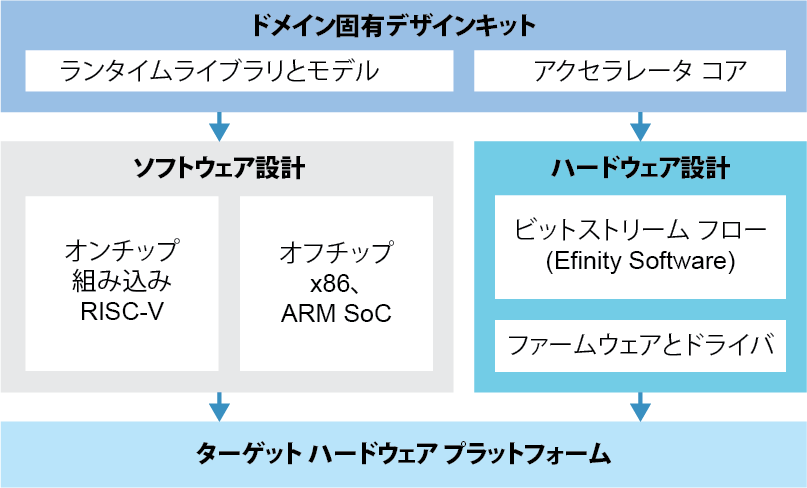

「RAP」の取り組みは、このように強化されたハードウェアの汎用性を補完するために、システム設計やソフトウェア・パーティショニングにおける直感的なアプローチを提供します。標準化されたハードウェア・アクセラレータ・インターフェイスにより、エフィニックス (Efinix) FPGA で利用可能な RISC-V コアを活用することができます。FPGA 内にハードウェア・アクセラレータを構築できるため、より直感的なハードウェア/ソフトウェア・パーティショニングが可能になり、市場投入までの時間が短縮され、システム性能が飛躍的に向上します。

エッジでの課題を解決

世界のデータ量は、2025 年には 175 ZB (ゼタバイト) に近づき、これらすべてのデータを収集、キャプチャ、変換、送信、およびその他の処理を行うデバイスの必要性が圧倒的に高まっています。今やデバイスはどこにでも存在しますが、電力や安定した帯域幅へのアクセスが制限された過酷な環境にある可能性があります。これらのデバイスは、大量のデータをローカルかつ安全にリアルタイム処理し、それを小さなスペースで、非常に少ない消費電力で実現することが求められています。これらの制約により、革新的なソリューションの必要性が高まっています。さらに、プロセスの微細化は、コストを指数関数的に増加させる結果となり、設計者は、次世代シリコンに頼るだけでは、市場投入までの時間的なニーズを満たすことはできません。

エッジ・アプリケーションは膨大で、混沌としており、多様で、進化しています。FPGA は構造上、市場投入された製品に組み込まれた後でもプログラム可能なため、必要要件の変化に柔軟に対応することができます。エッジでは、FPGA は現実世界の問題を解決するための完全なシステムを提供することができます。

収録されたウェビナー: Accelerating Edge Computing with FPGAs