RISC-V is an open-source standard instruction set architecture (ISA) that is managed by the non-profit RISC-V Foundation. This modular ISA has a base instruction set and optional extension sets. Because RISC-V is free and open-source, it has gained popularity worldwide. Over 65 RISC-V cores, both commercial and open-source, are available today.

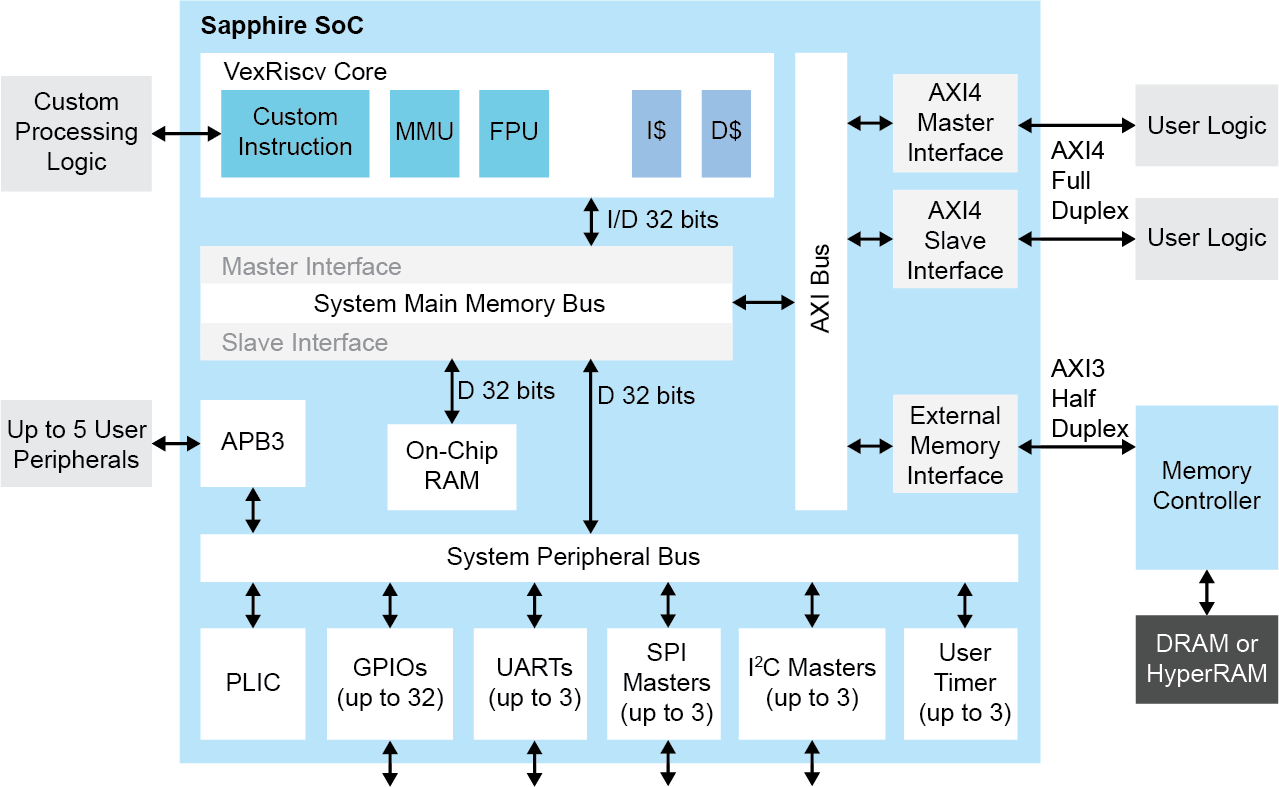

Efinix has created 3 RISC-V SoCs based on the VexRiscv core created by Charles Papon. The VexRiscv core, which won first place in the RISC-V SoftCPU contest in 2018, is a 32-bit CPU using the ISA RISCV32I with M and C extensions, has five pipeline stages (fetch, decode, execute, memory, and writeback), and a configurable feature set. Each SoC has a RISC-V processor, memory, a range of I/O, and interfaces for embedding user functions. You can easily create entire systems that include embedded compute and user-defined accelerators all in the same Titanium or Trion® FPGA.

- ~3K - 12K LEs, 8 - 179 RAM blocks

- 10 - 400 MHz

- 1.16 DMIPS/MHz

- Optional memory controller for DDR or HyperRAM memories with module sizes from 4 MB to 3.5 GB

- 4 - 512 KB on-chip RAM

- Up to 32 GPIO

- Timer

- PLIC

- Up to 3 SPI masters

- Up to 3 I2C masters

- Up to 3 UARTs

- Up to 2 AXI4 master channels

- 1 optional AXI4 user peripheral

- Up to 5 APB3 user peripherals

User-configurable, high-performance SoC with an optional memory controller. You can choose which peripherals you want by configuring the SoC in the Efinity IP Manager. This flixibility makes the Sapphire SoC ideal for a wide range of embedded applications.

Included with the Efinity IP Manager v2021.1 and higher

What's in the Package?

With each RISC-V SoC, Efinix provides a complete package of hardware and software files. Additionally, to help you develop software applications, Efinix distributes a collection of pre-compiled open-source software. With these packages, you can:

- Build RTL designs using the Sapphire, Ruby, Jade, or Opal RISC-V SoC using an example design targeting an Efinix development board, and learn how to extend the example for your own application.

- Set up the software development environment using an example project, create your own software based on example projects, and use the provided API.

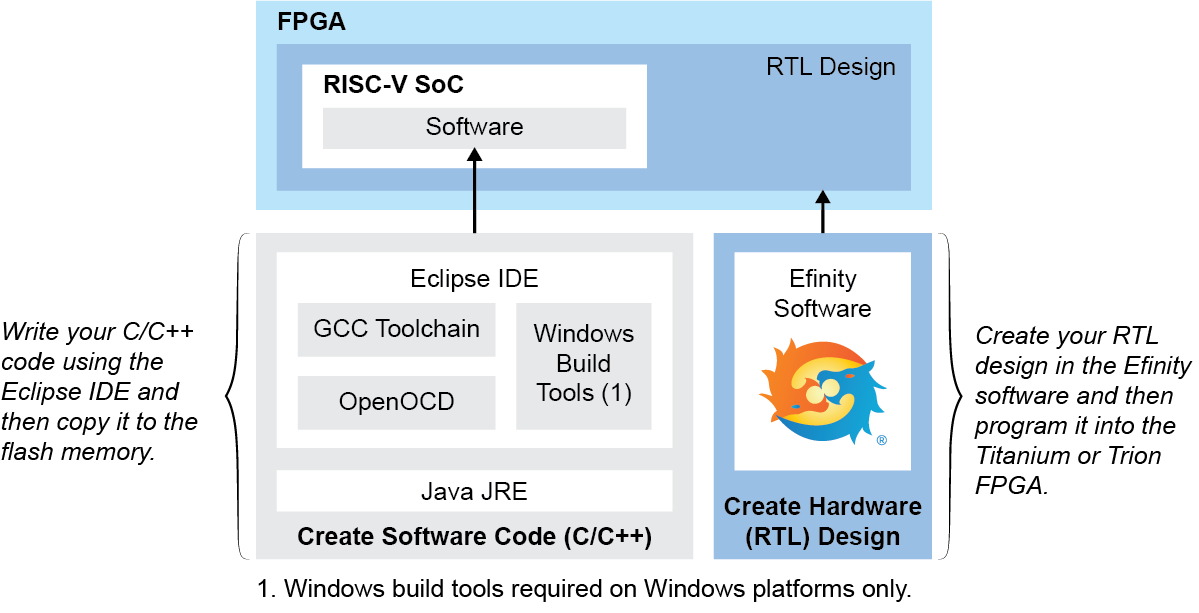

SoC Design Flow

Hardware

- SoC RTL files

- SoC testbench

- Example design targeting an Efinix development board

- Included with Efinity software

Software

- Board support package (BSP)

- Linker script

- SoC include header files

- OpenOCD configuration files

- Example software applications

- Included with the Efinity software

SDK

- Eclipse IDE for managing projects and software

- GCC compiler

- OpenOCD debugger for debugging

- Windows build tools (Windows)

- Download from the Support Center

Efinity Software Support

The SoCs are fully supported by the Efinity® software, which provides a complete tool flow from RTL design to bitstream generation, including synthesis, place-and-route, debugging, and timing analysis. The software has a graphical user interface (GUI) that provides a visual way to set up projects, run the tool flow, and view results. The software also has a command-line flow and Tcl command console. The software-generated bitstream file configures Trion devices. The software supports the Verilog HDL and VHDL languages.

RISC-V Overview

This video provides talks about our soft RISC-V SoCs, and RISC-V based solutions and accelerators to help you get your edge design to market quickly with Efinix FPGAs.